# Describing and Simulating Dynamic Reconfiguration in SystemC Exemplified by a Dedicated 3D Collision Detection Hardware

Dissertation

zur Erlangung des Doktorgrades (Dr. rer. nat.) der Mathematisch-Naturwissenschaftlichen Fakultät der Rheinischen Friedrich-Wilhelms-Universität Bonn

> vorgelegt von Diplom Informatiker Andreas Raabe aus Niederkassel

> > Bonn, April 18, 2008

Reviewer: Joachim K. Anlauf, Reinhard Klein Date of oral exam: August 10, 2008 Published: 2008

Diese Dissertation ist auf dem Hochschulschriftenserver der ULB Bonn unter http://hss.ulb.uni-bonn.de/diss\_online elektronisch publiziert. This dissertation is publicly available on the server of the ULB Bonn at http://hss.ulb.uni-bonn.de/diss\_online in elecronic form.

This work was typeset with  $\mathsf{KOMA}\text{-}\mathsf{Script}$  and  $\operatorname{I\!AT}_{\!E\!X}\!.$

For my parents, who provided me such a fine start in life.

And for Silke, who loves me how I am.

| I  | Introduction |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13 |  |

|----|--------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 1  |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |  |

| 2  |              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |  |

|    | 2.2          |              | jective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |

|    | 2.3          |              | action Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |

|    | 2.4          | 0            | ation Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |  |

|    | 2.5          | v            | esis Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |

|    | 2.6          |              | ctivity Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |  |

|    | 2.7          | Case-S       | Study Objective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 21 |  |

| 3  | Cho          | ice of C     | Case Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23 |  |

| 4  | Orga         | anisatio     | un and a state of the state of | 25 |  |

|    | 4.1          | Docum        | nent Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25 |  |

|    | 4.2          | Specifi      | ic Terms Used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25 |  |

| 11 | De           | scribin      | g and Simulating Dynamic Reconfiguration in SystemC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27 |  |

| 5  | Related Work |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |  |

|    | 5.1          | Basics       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 29 |  |

|    |              | 5.1.1        | SystemC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29 |  |

|    |              |              | A Brief SystemC Methodology Recap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29 |  |

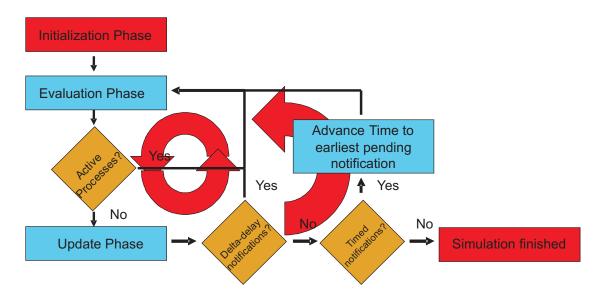

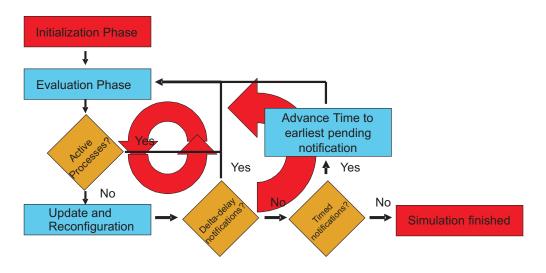

|    |              |              | SystemC Simulation Semantics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 32 |  |

|    |              |              | Elaboration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 32 |  |

|    |              |              | Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 34 |  |

|    |              | 5.1.2        | Reconfigurable Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |  |

|    |              |              | Xilinx Virtex                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |  |

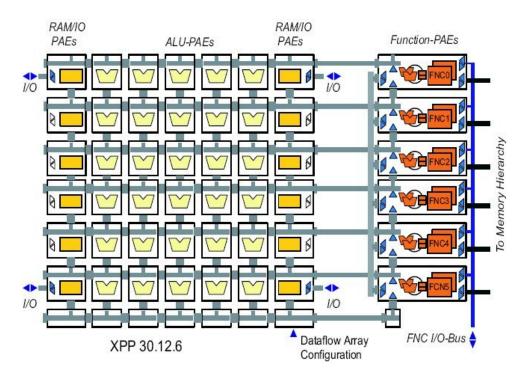

|    |              |              | PACT XPP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |  |

|    | <b>_</b> -   |              | Conclusion - Architecture Specific Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |  |

|    | 5.2          | 0            | Level Reconfiguration Modelling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |  |

|    |              | 5.2.1        | JHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |  |

|    |              | <b>Z</b> 0 0 | Conclusion on JHDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |  |

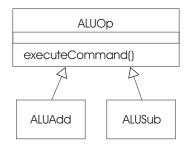

|    |              | 5.2.2        | OSSS+R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39 |  |

|     |                             | OSSS                                                     | 39 |

|-----|-----------------------------|----------------------------------------------------------|----|

|     |                             | Modelling Reconfiguration with $OSSS+R$                  | 41 |

|     |                             | The OSSS+R Reconfiguration Controller                    | 44 |

|     |                             | Conclusion                                               | 44 |

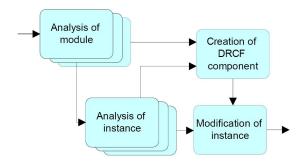

|     | 5.2.3                       | DRCF                                                     | 45 |

|     |                             | DRCF Approach                                            | 45 |

|     |                             | Conclusion on DRCF                                       | 47 |

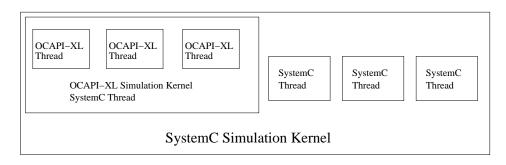

|     | 5.2.4                       | OCAPI-XL                                                 | 49 |

|     |                             | Reconfigurable Context Switching                         | 50 |

|     |                             | Conclusion on OCAPI-XL                                   | 51 |

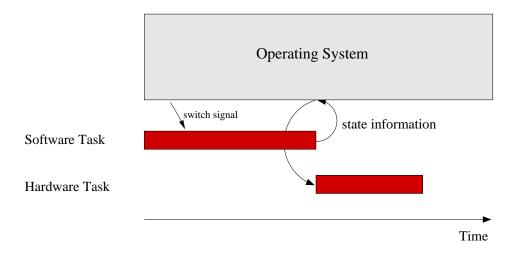

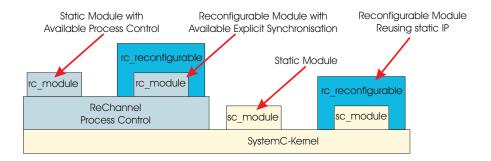

|     | 5.2.5                       | Process Control                                          | 51 |

|     |                             | Concluding Remarks on Process Control Kernels            | 52 |

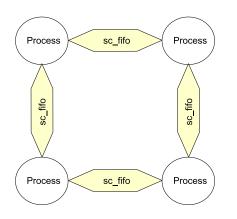

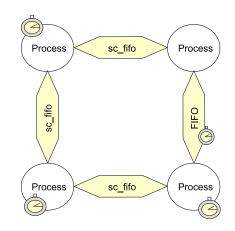

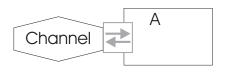

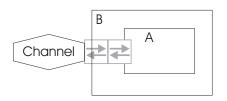

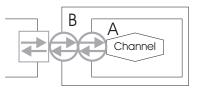

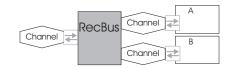

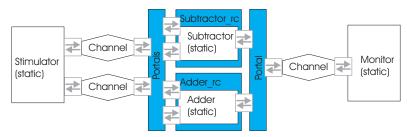

| The |                             | annel Approach                                           | 53 |

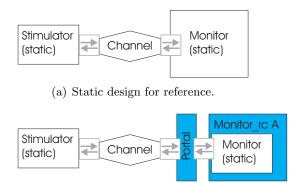

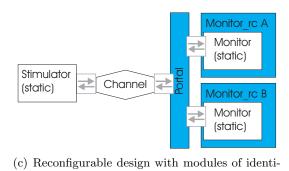

| 6.1 |                             | IANNEL- Basic Features                                   |    |

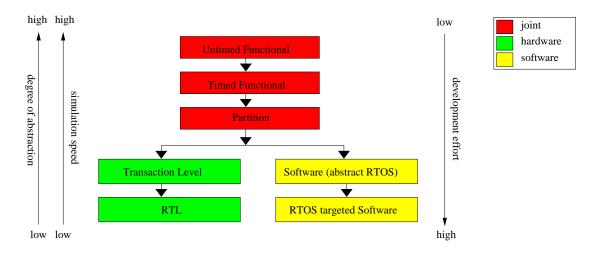

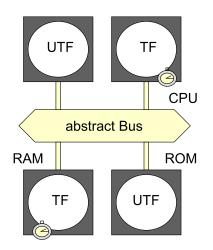

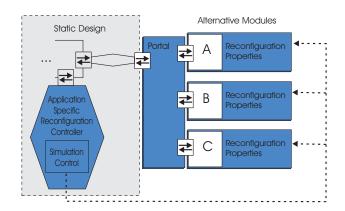

|     | 6.1.1                       | Modelling Reconfiguration on All Levels of Abstraction   | 55 |

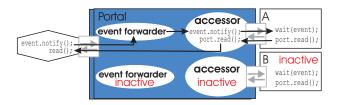

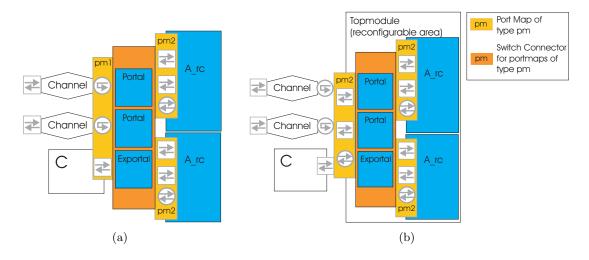

|     |                             | Using Portals To Intercept Communication                 | 55 |

|     |                             | Creating Custom Portals                                  | 58 |

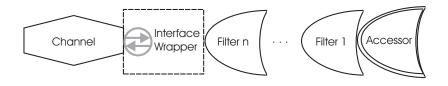

|     |                             | Interface Wrapper                                        | 60 |

|     |                             | Reconfiguration Callbacks                                | 61 |

|     | 6.1.2                       | Rendering Own Components and Third-Party IP Cores Recon- |    |

|     |                             | figurable                                                | 62 |

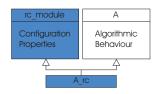

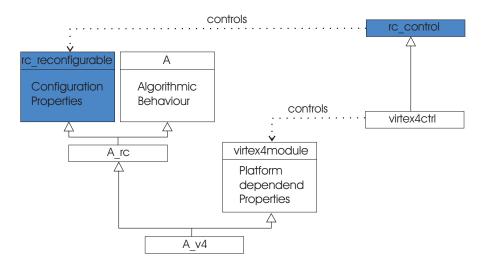

|     |                             | Creating Reconfigurable Modules                          | 64 |

|     |                             | The Module's States                                      | 64 |

|     |                             | State Preservation                                       | 67 |

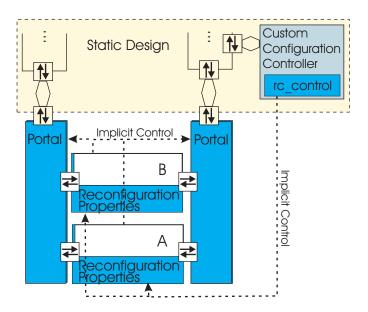

|     | 6.1.3                       | Controlling Reconfiguration Simulation Control           | 67 |

|     |                             | Operating on Sets of Modules                             | 68 |

|     |                             | Intermediate Recap                                       | 68 |

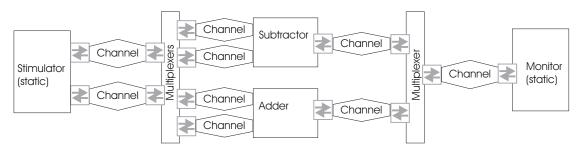

| 6.2 | Advanced ReChannel Features |                                                          | 71 |

|     | 6.2.1                       | Reconfigurable Overhead In Static Applications           | 71 |

|     | 6.2.2                       | Accuracy of Reconfiguration Delays                       | 72 |

|     | 6.2.3                       | Exportals                                                | 74 |

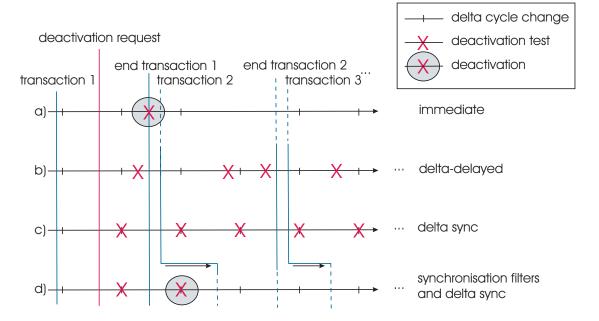

|     | 6.2.4                       | Synchronisation Filters                                  | 75 |

|     |                             | Transaction Counters                                     | 77 |

|     |                             | Filter Callbacks                                         | 77 |

|     |                             | Full Implementation of a Synchronisation Filter          | 77 |

|     | 6.2.5                       | Explicit Description of Reconfiguration                  | 79 |

|     |                             | Resettable Processes                                     | 80 |

|     |                             | Resettable Components                                    | 82 |

|     | 6.2.6                       | Binding Groups of Switches                               | 83 |

| 6.3 | ReCh                        | IANNEL Simulation Semantics                              | 84 |

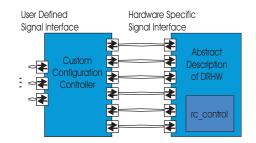

| 6.4 | Integr                      | ating Reconfiguration into the Refinement Process        | 87 |

|     | 6.4.1                       | Functional Level                                         | 87 |

|     |                             |                                                          |    |

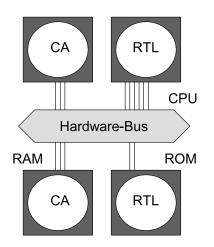

|   |      | $6.4.2 \\ 6.4.3$ | Transactional Level       Register Transfer Level     | 88<br>88 |

|---|------|------------------|-------------------------------------------------------|----------|

|   | Α    | Dedica           | ted 3D Collision Detection FPGA Architecture          | 91       |

| 7 |      | ted Wo           |                                                       | 93       |

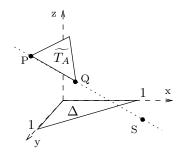

|   | 7.1  |                  | on Detection Overview                                 | 93       |

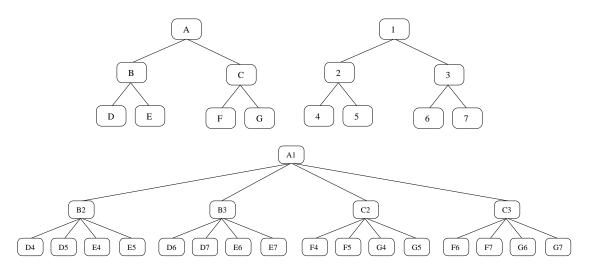

|   | 7.2  |                  | chical Collision Detection                            | 94       |

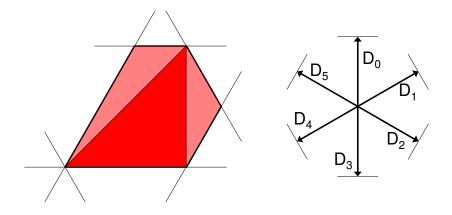

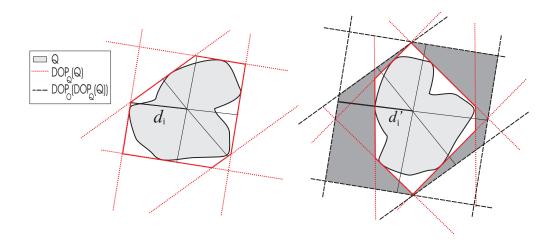

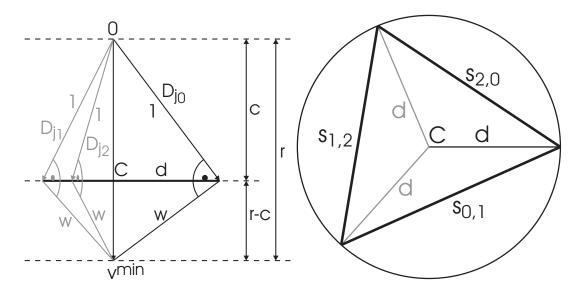

|   | 7.3  |                  | $\mathbf{P}_{\mathbf{S}}$                             | 95       |

|   | 7.4  | -                | ating Axis Test - SAT                                 | 96       |

|   | 7.5  |                  |                                                       | 97       |

|   | 7.6  |                  | SIC Targeted Approach                                 | 97       |

|   |      | 7.6.1            | Bounding Volume Test                                  | 97       |

|   |      | $7.6.2 \\ 7.6.3$ | Triangle Intersection                                 |          |

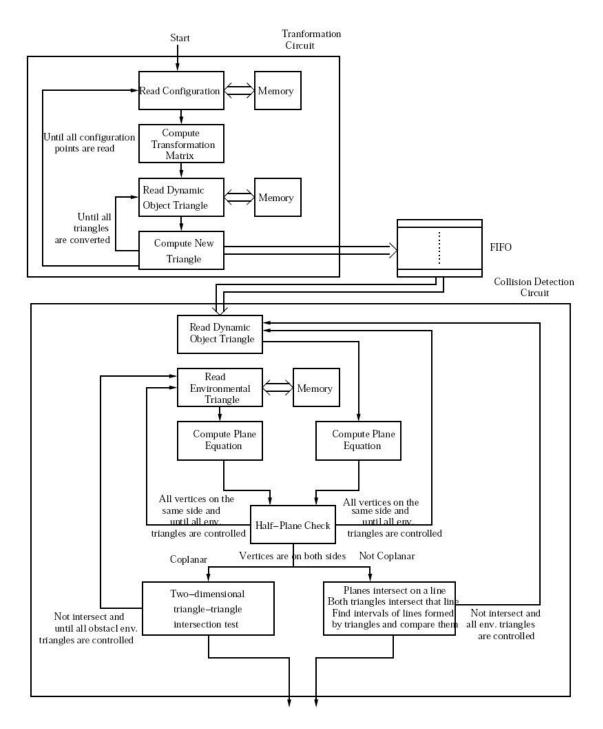

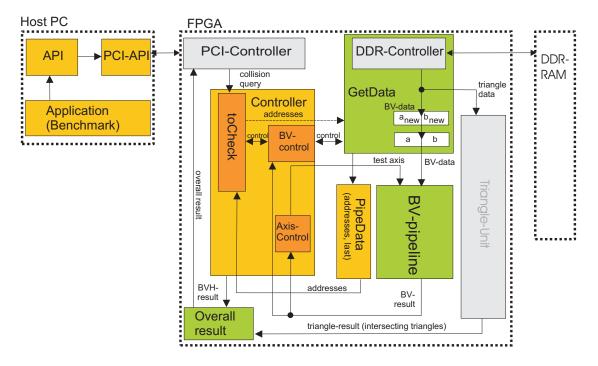

|   |      | 1.0.5            | The Architecture    DOP Architecture                  |          |

|   |      |                  | Control                                               |          |

|   |      |                  | Triangle Architecture                                 |          |

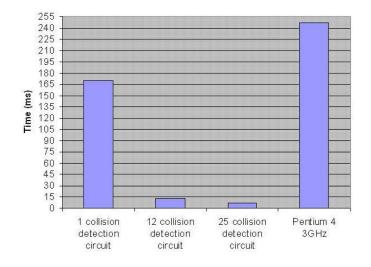

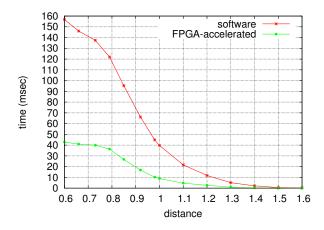

|   |      |                  | Performance Evaluation                                |          |

|   |      | 7.6.4            | Conclusion                                            |          |

|   | 7.7  |                  | -Accelerated Möller Triangle-Intersection Test        |          |

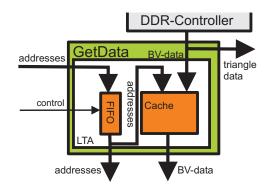

|   |      | 7.7.1            | Preprocessing, I/O and Memory Interface               |          |

|   |      | 7.7.2            | The Architecture                                      |          |

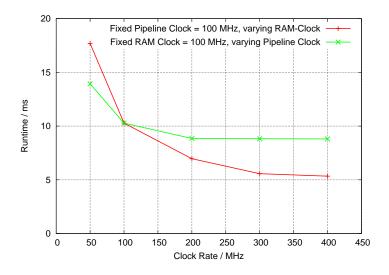

|   |      | 7.7.3            | Performance Evaluation                                |          |

|   |      | 7.7.4            | Conclusion                                            | 110      |

| 8 | Call | ision Ch         | ip: An FPGA-Based 3D Collision Detection Architecture | 113      |

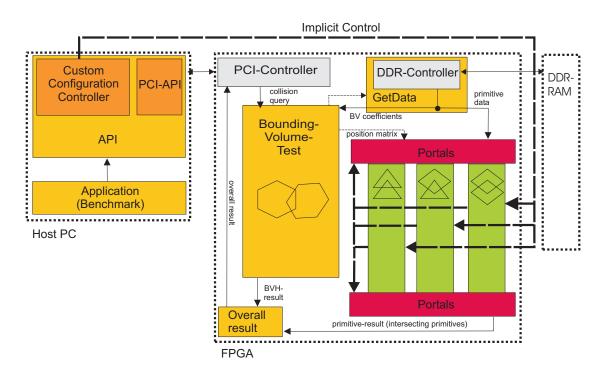

| 0 | 8.1  |                  | Efficient Collision Detection                         |          |

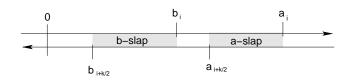

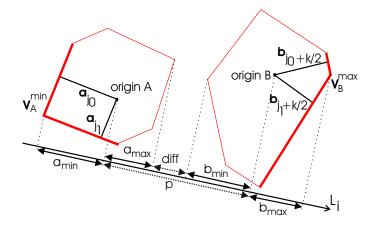

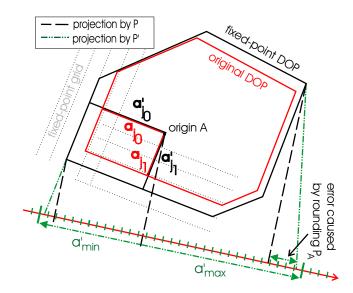

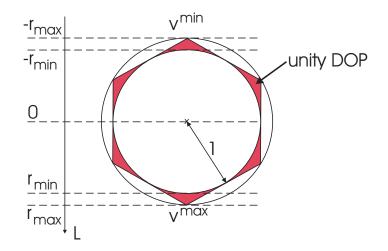

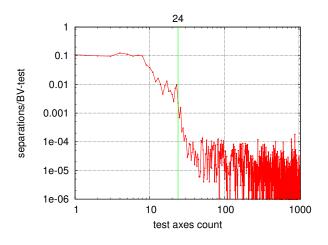

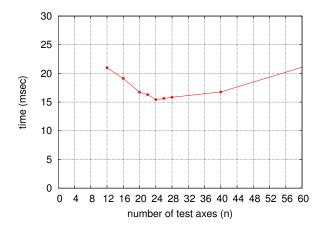

|   | 0.1  | 8.1.1            | Efficient SAT for k-DOPs                              |          |

|   |      | 0.1.1            | Precomputation                                        |          |

|   |      |                  | Intersection Testing                                  |          |

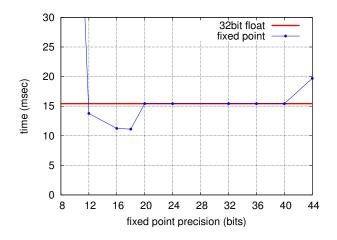

|   |      | 8.1.2            | Fixed-Point Arithmetic                                |          |

|   |      | 0.1.2            | Correct Fixed-Point Rounding                          |          |

|   |      |                  | Bound on Fixed-Point Deviation                        |          |

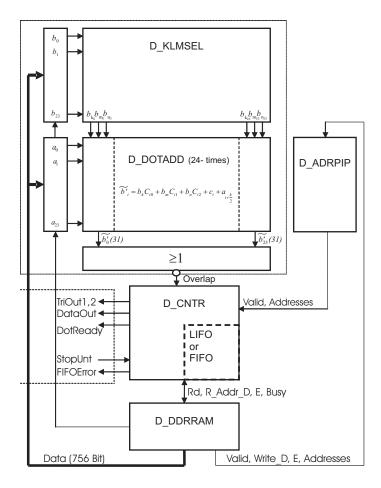

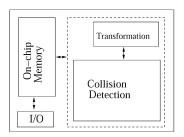

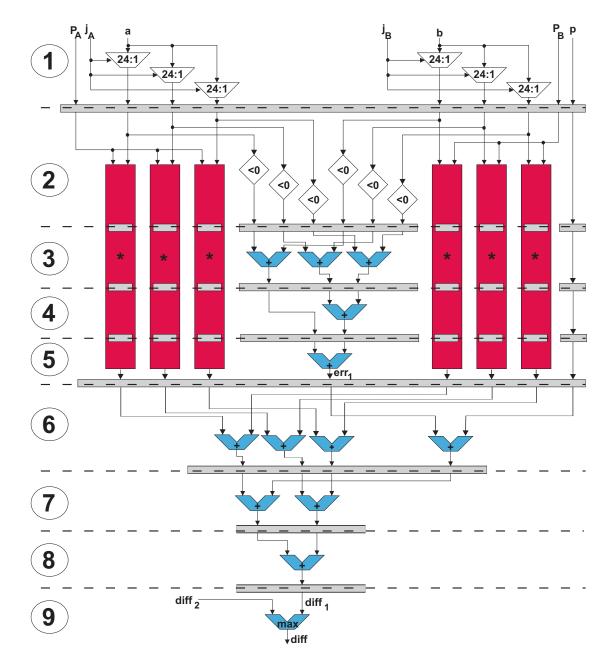

|   | 8.2  | The A            | rchitecture                                           |          |

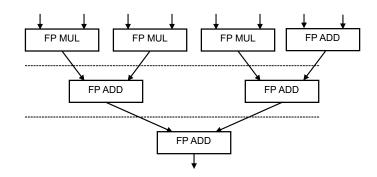

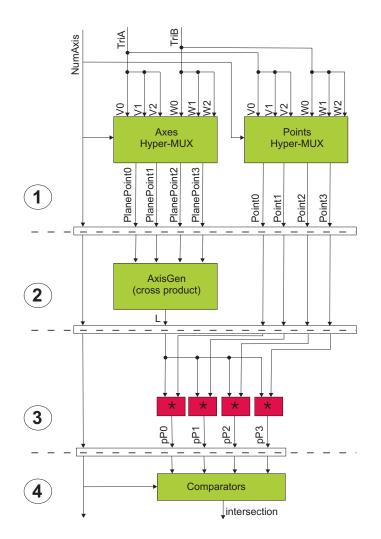

|   |      | 8.2.1            | The Pipeline                                          |          |

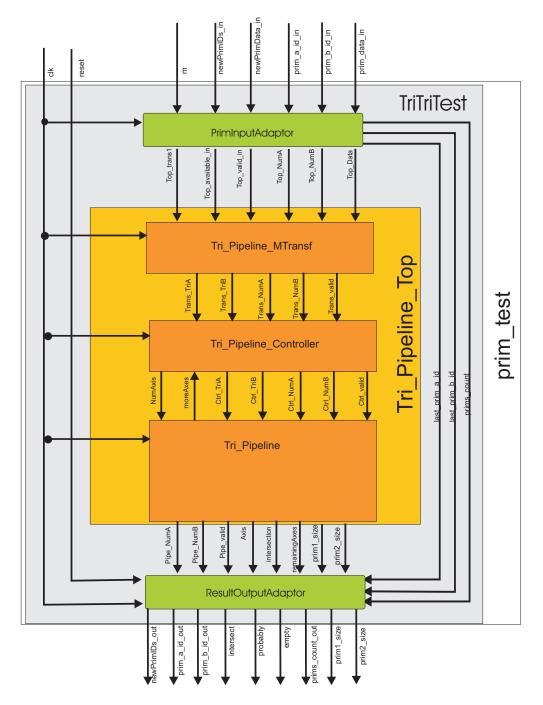

|   |      | 8.2.2            | Overall Design                                        |          |

|   | 8.3  | Contro           |                                                       |          |

|   |      | 8.3.1            | Push and Pull Control Architecture                    |          |

|   |      | 8.3.2            | Input FIFO                                            |          |

|   |      | 8.3.3            | Optimizing Tree Traversal                             |          |

|   | 8.4  | Result           | s of the Basic Architecture                           |          |

|   |      | 8.4.1            | Synthesis Results                                     |          |

|     | 8.4.2  | Benchmarking                                                         |

|-----|--------|----------------------------------------------------------------------|

| 8.5 | Defyir | ng the Memory Bottleneck                                             |

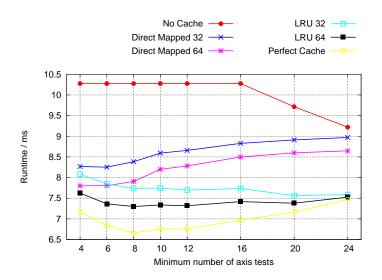

|     | 8.5.1  | Investigating on Benefits of Caching                                 |

|     | 8.5.2  | Comparing Caching Techniques                                         |

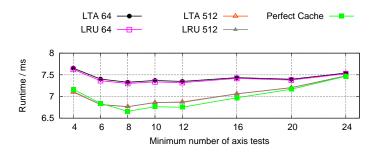

|     |        | LTA Cache                                                            |

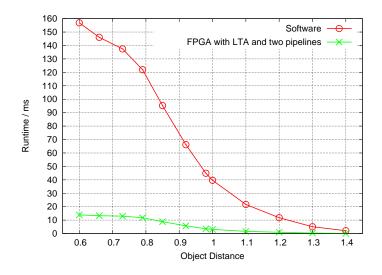

|     | 8.5.3  | Performance Evaluation and Synthesis Results of the LTA Cache . 134  |

| 8.6 | Synthe | esis and Implementation                                              |

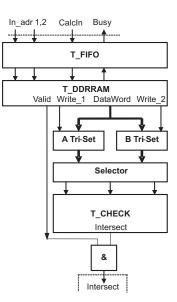

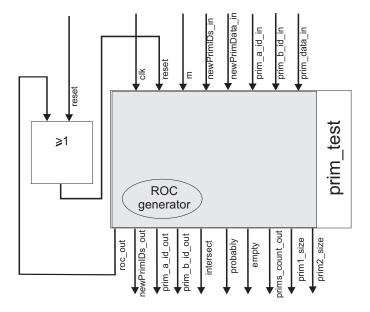

| 8.7 | The P  | rimitive Test Subsystem                                              |

|     | 8.7.1  | Triangle Intersection Test Review                                    |

|     |        | $2\times 2$ Linear Equation System, Configuration Space and Determi- |

|     |        | nants Approaches                                                     |

|     |        | Triangle Transformation                                              |

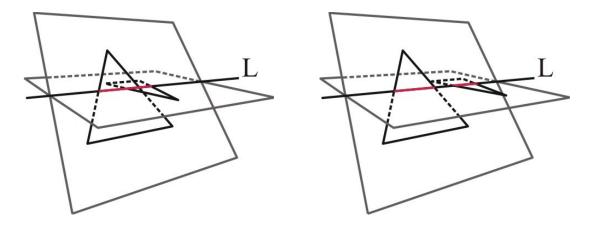

|     |        | Common Line Intervals                                                |

|     |        | SAT for Triangle Intersection Testing                                |

|     |        | Choice of Triangle Intersection Test                                 |

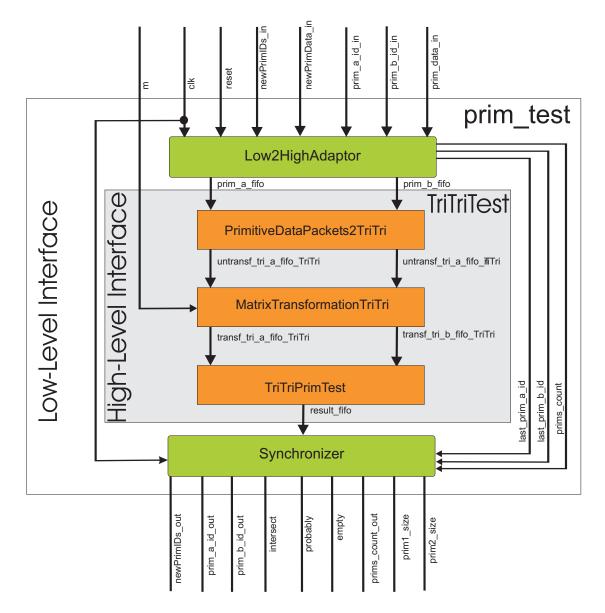

|     | 8.7.2  | Integrating the Primitive Test into the Overall Design 141           |

|     |        | Untimed Functional Implementation of SAT for the Primitives 141      |

|     |        | Primitive SAT on RT-Level                                            |

|     |        | The Intersection Test Pipeline                                       |

|     |        | Synthesis Results of the Primitive Intersection Test 146             |

|     |        |                                                                      |

147

# IV Putting It All Together

| App  | lying R                                                 | eChannel To CollisionChip                                                                                                                                                                                                                                                                                                                                  | 149                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

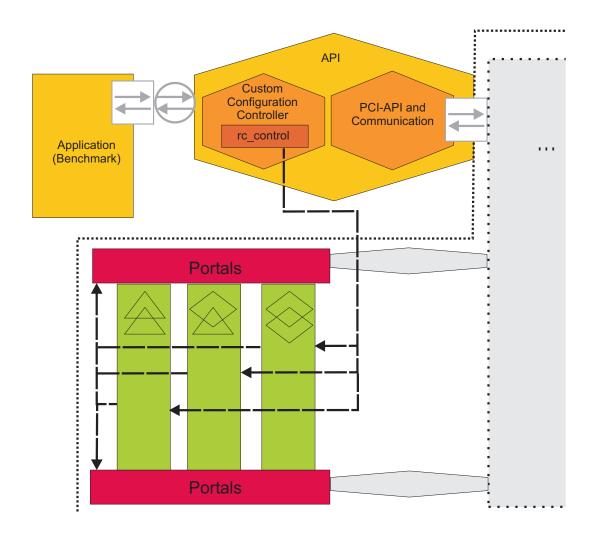

| 9.1  | Untime                                                  | ed Functional Level                                                                                                                                                                                                                                                                                                                                        | 150                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 9.1.1                                                   | Reconfigurable Topology                                                                                                                                                                                                                                                                                                                                    | . 150                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 9.1.2                                                   | Reconfiguration Control                                                                                                                                                                                                                                                                                                                                    | 152                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 9.1.3                                                   | Synchronisation                                                                                                                                                                                                                                                                                                                                            | 152                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9.2  | Timed                                                   | Functional Level                                                                                                                                                                                                                                                                                                                                           | 155                                                                                                                                                                                                                                                                                                                                                                                                                 |

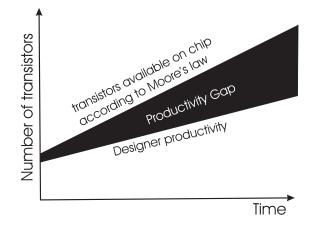

| 9.3  | Transa                                                  | action Level                                                                                                                                                                                                                                                                                                                                               | 155                                                                                                                                                                                                                                                                                                                                                                                                                 |