# Evaluation of a Serial Powering Scheme and its Building Blocks for the ATLAS ITk Pixel Detector

Dissertation

zur

Erlangung des Doktorgrades (Dr. rer. nat.)

der

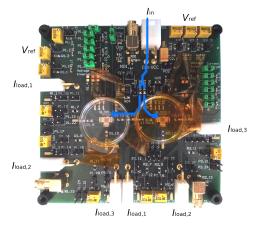

Mathematisch-Naturwissenschaftlichen Fakultät

der

Rheinischen Friedrich-Wilhelms-Universität Bonn

von

Florian Hinterkeuser

aus

Jena

Bonn, 2022

|                                                                                                           | nmigung der Mathematisch-Naturwissenschaftlichen Fakultät der<br>n-Wilhelms-Universität Bonn |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| <ol> <li>Gutachter:</li> <li>Gutachter:</li> <li>Tag der Promotion:</li> <li>Erscheinungsjahr:</li> </ol> | Prof. Dr. Klaus Desch<br>Prof. Dr. Jochen Dingfelder<br>23.09.2022<br>2022                   |

# **Abstract**

The high luminosity upgrade for the Large Hadron Collider (LHC) at CERN requires a complete redesign of the current inner detectors of ATLAS and CMS. These new inner detectors will consist of all-silicon tracking detectors, combining multiple layers of silicon hybrid pixel modules and strip detectors. In the new pixel detectors conservative powering schemes are not feasible anymore. Instead serial powering has been chosen as a baseline powering scheme for both the future ATLAS and CMS pixel detectors. In serial powering, multiple detector modules are powered by a constant supply current. This new powering scheme provides challenges for the electrical and mechanical design, from the readout chip to system level considerations.

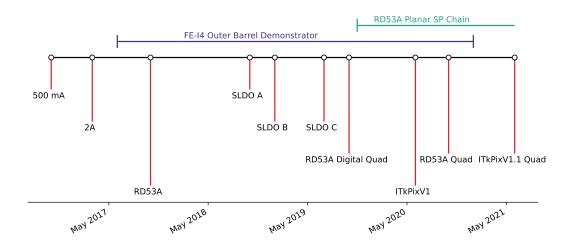

The main building block of the serial powering scheme foreseen for the ATLAS ITk pixel detector is the shunt low dropout voltage regulator (Shunt-LDO). The Shunt-LDO generates the local supply voltages for each pixel module from the constant supply current while shunting any excess current not drawn by the readout chips. In this thesis the Shunt-LDO is extensively characterised and evaluated. The expanding feature set of the Shunt-LDO has been verified over several years of development and the radiation hardness of the regulator design in the 65 nm CMOS process node used for the ATLAS ITk pixel readout chips has been proven. The operation and performance of next-generation pixel readout chips using the Shunt-LDO was demonstrated using RD53A, a technology demonstrator for the future ATLAS and CMS pixel readout chips.

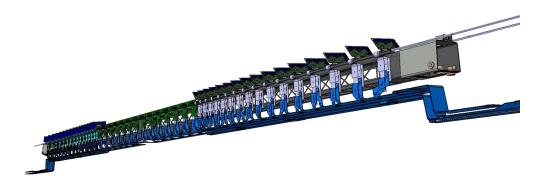

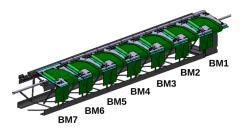

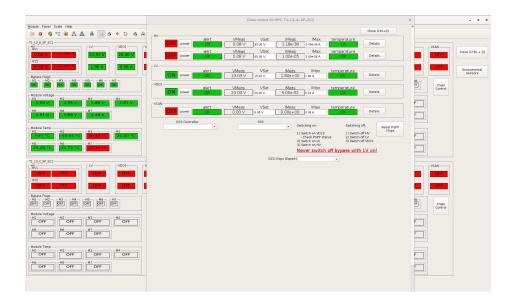

An additional focus of this work is the large scale prototyping of serial powering. In the context of this work the Outer Barrel Demonstrator (OBD) program at CERN was commissioned and yielded first valuable experiences in operating a serially powered pixel detector with representative services and local supports. The OBD was the first prototype to operate multiple parallel, electrically coupled serial powering chains successfully. Finally a serial powering chain with pixel detector modules based on the next-generation readout chip, the RD53A, has been scoped, designed and set up in the context of this thesis with the goal to study low-level properties of serially powered detectors. This prototype, consisting of 8 RD53A quad chip modules with planar silicon sensors, demonstrated the ability to operate a serial powering chain with modules based on the next-generation readout chips without any performance deterioration.

# **Contents**

| 1 | Intro | ductio                                                                  | n                                                                  | 1  |  |  |

|---|-------|-------------------------------------------------------------------------|--------------------------------------------------------------------|----|--|--|

|   | 1.1   | The La                                                                  | arge Hadron Collider                                               | 2  |  |  |

|   |       | 1.1.1                                                                   | The High-Luminosity LHC                                            | 4  |  |  |

|   | 1.2   | The A                                                                   | TLAS Experiment                                                    | 5  |  |  |

|   |       | 1.2.1                                                                   | The ATLAS Inner Detector                                           | 7  |  |  |

|   |       | 1.2.2                                                                   | The ATLAS Phase 2 Upgrade and the ITk Project                      | 9  |  |  |

| 2 | Silic | on Pixe                                                                 | el Detectors in High Energy Physics                                | 13 |  |  |

|   | 2.1   | Silicon                                                                 | Particle Detectors                                                 | 14 |  |  |

|   |       | 2.1.1                                                                   | Particle Interaction with Matter                                   | 14 |  |  |

|   |       | 2.1.2                                                                   | Signal Generation and Detection                                    | 16 |  |  |

|   |       | 2.1.3                                                                   | Spatial Resolution                                                 | 18 |  |  |

|   |       | 2.1.4                                                                   | Signal Processing                                                  | 19 |  |  |

|   | 2.2   |                                                                         |                                                                    |    |  |  |

|   |       | 2.2.1                                                                   | Modules                                                            | 21 |  |  |

|   |       | 2.2.2                                                                   | Services                                                           | 22 |  |  |

| 3 | Seri  | al Powe                                                                 | ering - A Novel Powering Scheme for the ITk Pixel Detector         | 27 |  |  |

|   | 3.1   | Serial                                                                  | Powering Concept                                                   | 28 |  |  |

|   |       | 3.1.1                                                                   | AC-Coupling of Data Signals                                        | 31 |  |  |

|   |       | 3.1.2                                                                   | High Voltage Distribution                                          | 33 |  |  |

|   | 3.2   | Voltag                                                                  | e Regulation with the Shunt-LDO Regulator                          | 35 |  |  |

| 4 | The   | Shunt-l                                                                 | _DO for a new Generation of Pixel Readout Chips with Serial Power- |    |  |  |

|   | ing   | Capabil                                                                 | ity                                                                | 41 |  |  |

|   | 4.1   | Prototyping and Characterization of a Shunt-LDO in a 65 nm Node for the |                                                                    |    |  |  |

|   |       | RD53.                                                                   | A Readout Chip                                                     | 42 |  |  |

|   |       | 4.1.1                                                                   | 500 mA prototype                                                   | 43 |  |  |

|   |       | 112                                                                     | 2 A prototyne                                                      | 56 |  |  |

| 4.2 RD53A - A Prototype Readout ASIC with Serial Powering Capability |             |                                                                               | 65 |

|----------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------|----|

|                                                                      |             | 4.2.1 The Shunt-LDO in RD53A                                                  | 67 |

|                                                                      | 4.3         | An Updated Shunt-LDO Design for RD53B                                         | 74 |

|                                                                      |             | 4.3.1 Characterisation of the new Shunt-LDO Prototype                         | 80 |

|                                                                      | 4.4         | Conclusion and Outlook Towards the ATLAS Production Chip                      | 94 |

| 5                                                                    | Larg        | e Scale Serial Powering Prototypes for the ITk Pixel Detector                 | 97 |

|                                                                      | 5.1         | The Outer Barrel Demonstrator Program                                         | 99 |

|                                                                      |             | 5.1.1 A Small Electrical Prototype                                            | 00 |

|                                                                      |             | 5.1.2 The Outer Barrel Demonstrator                                           | 06 |

|                                                                      |             | 5.1.3 Conclusion and Outlook                                                  | 98 |

|                                                                      | 5.2         | Setup of a Serial Powering Prototype with RD53A Modules                       | 10 |

|                                                                      |             | 5.2.1 An RD53A Quad Module for Serial Chain Operation                         | 10 |

|                                                                      |             | 5.2.2 Services and Periphery                                                  | 19 |

|                                                                      | 5.3         | Characterisation of a Serial Powering Chain with Planar RD53A Quad Modules 12 | 24 |

|                                                                      |             | 5.3.1 Quad Module Reception Tests                                             | 24 |

|                                                                      |             | 5.3.2 Electrical Characteristics of Modules                                   | 25 |

|                                                                      |             | 5.3.3 Shunt-LDO Current Headroom                                              | 32 |

|                                                                      |             | 5.3.4 Module Performance in Serial Powering chain                             | 35 |

|                                                                      |             | 5.3.5 Studies of the HV Distribution                                          | 41 |

|                                                                      |             | 5.3.6 Conclusion and outlook                                                  | 46 |

| 6                                                                    | Sum         | mary and Outlook 14                                                           | 49 |

| A                                                                    | App         | endix - Shunt-LDO Characterization                                            | 53 |

|                                                                      | <b>A.</b> 1 | 2 A Prototype                                                                 | 54 |

|                                                                      | A.2         | RD53A                                                                         | 55 |

|                                                                      | A.3         | RD53B Test Chip B                                                             | 59 |

|                                                                      | A.4         | RD53B Test Chip B Irradiation                                                 | 62 |

|                                                                      |             | A.4.1 Cold Irradiation Campaign                                               | 52 |

|                                                                      |             | A.4.2 Warm Irradiation Campaign                                               | 69 |

| В                                                                    | App         | endix - Large Scale Serial Powering Prototypes for the ITk Pixel Detector 1   | 73 |

|                                                                      | <b>B</b> .1 | An RD53A Quad Module for Serial Chain Operation                               | 74 |

|                                                                      | <b>B.2</b>  | Reception Tests                                                               | 77 |

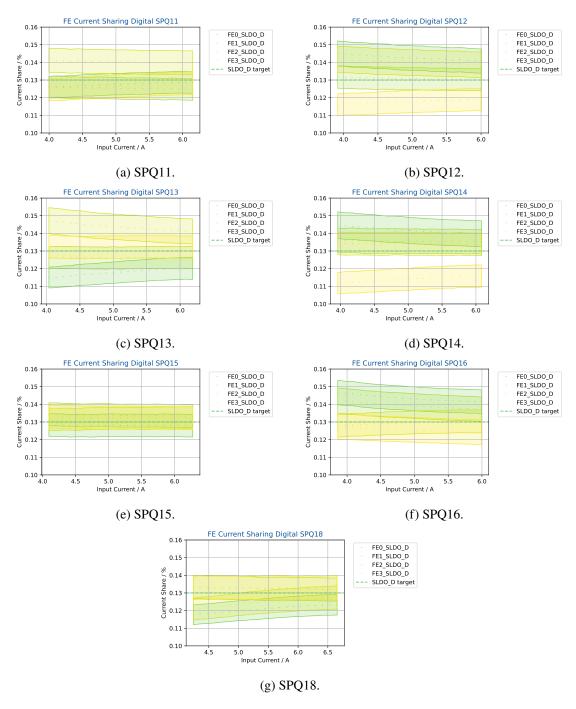

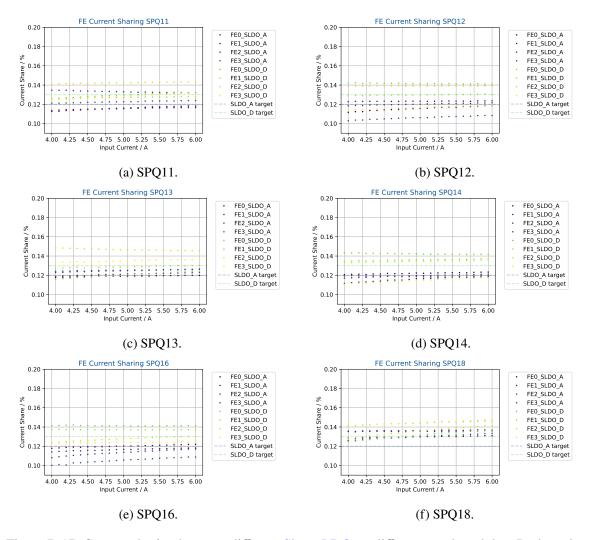

|                                                                      | <b>B</b> .3 | Characterisation of an RD53A Serial Powering Chain: Shunt-LDO Meas-           |    |

|                                                                      |             | urements                                                                      | 79 |

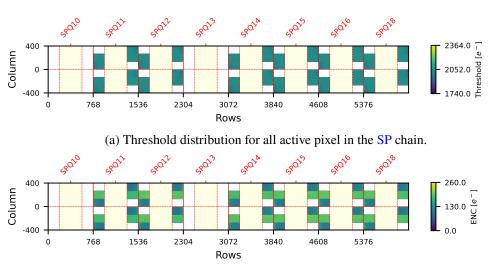

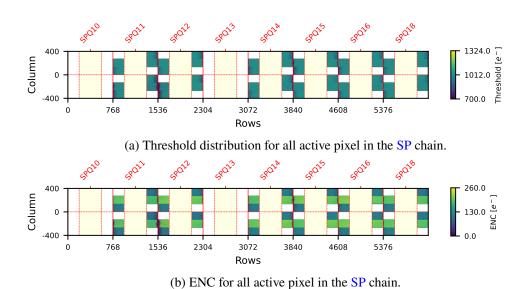

|                                                                      | <b>B.4</b>  | Characterisation of an RD53A Serial Powering Chain: Module Performance        |    |

|                                                                      |             | in a Serial Powering Chain                                                    | 93 |

| B.5 High Voltage Off Mode Studies | 195 |

|-----------------------------------|-----|

| Bibliography                      | 197 |

| List of Figures                   | 205 |

| List of Tables                    | 219 |

| Glossary                          | 223 |

| Acronyms                          | 225 |

| Acknowledgements                  | 229 |

# CHAPTER 1

# Introduction

A major driving factor for humanity is the constant pursuit of knowledge, striving towards an understanding of the universe we live in - from the largest of structures in the cosmos, macroscopic phenomena in nature and society, down to the very building blocks of nature. Modern particle physics contributes to this quest, aiming to investigate the fundamental structure of matter, the (elementary) particles and their interactions.

Ironically, the investigation of the smallest particles known to exist requires experiments of unprecedented scale. In these experiments, particles are accelerated close to the speed of light and collide at tremendous energies, creating an environment similar to the immediate aftermath of the birth of the universe. In these collisions new particles are created. These particles often are not stable and decay within fractions of a fraction of a second. Nonetheless, their decay products can be detected using modern particle detectors. The properties of the particles created offer insights in the underlying physics processes and fundamental forces involved. Unfortunately interactions suited to probe and improve modern particle physics theories, most prominently the Standard Model of particle physics, are very rare and require many collisions to ever be recorded.

The most prominent example in recent times was the discovery of the Higgs boson in 2012 at the Large Hadron Collider (LHC) [1, 2]. More than 1 000 000 000 particle collisions were required on average to produce a single Higgs boson. The detectors tasked to record these rare particle signatures and their decay products need to be highly sensitive and fast, all while being exposed to a harsh environment. The two general purpose experiments are the A Toroidal LHC ApparatuS (ATLAS) and Compact-Muon-Solenoid (CMS) detectors at the LHC. They move at the forefront of technology, demanding new innovations and providing opportunities for new developments in many fields, from the design of integrated circuits to the engineering challenges of building large detectors. The next step in these developments is the upcoming luminosity upgrade of the LHC. This upgraded LHC will once again present

the experiments with unprecedented challenges, driving some of the most complex and ambitious projects in the history of particle physics. These challenges are tackled by the installation of upgraded detectors for both ATLAS and CMS. These massive projects - the ATLAS detector alone is comparable in size to roughly half the Notre Dame cathedral in Paris [3] - are undertaken by large international collaborations.

The focus in this thesis is on the upgrade of the innermost part of ATLAS - the tracking detector. The upgrade of this detector towards the new ATLAS Inner Tracker (ITk), introduced in Section 1.2.2, faces one of its most important challenges in the question of how to realize a high-performance, low material particle detector with acceptable power distribution efficiency. Conservative approaches to this very fundamental issue of delivering power to the detector will fail in the ITk pixel detector. Instead a novel approach has been chosen for the ITk pixel detector in Serial Powering, a concept introduced in Chapter 3.

Components and building blocks of this novel powering scheme have been in development over the past two decades and are reaching the maturity required for deployment in the ATLAS ITk pixel detector. One example for such a building block is the Shunt-LDO voltage regulator, a crucial part in the serial powering scheme employed by ATLAS. Chapter 4 presents contributions to this development in the characterisation and evaluation of the shunt low dropout voltage regulator (Shunt-LDO), from the first implementation in the new 65 nm technology to a mature implementation for the final application specific integrated circuit (ASIC) used in both the future ATLAS and CMS pixel detectors.

The implications of serial powering are however not limited to the scale of microelectronics. They require extensive prototyping on large scales to cover the system aspects of serial powering. These efforts are far beyond the scale of a single PhD thesis and involve large collaborations on their own. This work contributed to these efforts on mainly two aspects, both covered in Chapter 5: the Outer Barrel Demonstrator program at CERN as well as a small scale serial powering prototype, built from novel pixel detector ASICs in the SiLAB<sup>1</sup>, as part of the larger ATLAS system test community.

# 1.1 The Large Hadron Collider

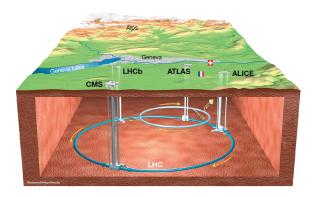

The LHC [4] is currently the largest and most powerful particle accelerator and largest machine ever built. It is built and operated by the European Organization for Nuclear Research (CERN) and located in the border region between France and Switzerland near Geneva. The LHC reuses the existing tunnel infrastructure of its direct predecessor LEP<sup>2</sup> between 45 m and 170 m underground. Figure 1.1 shows an overview of the scale and general location of

<sup>&</sup>lt;sup>1</sup> Silizium LAbor Bonn

<sup>&</sup>lt;sup>2</sup> Large Electron-Positron Collider, constructed in 1989 and decommissioned in 2000 in favour of the LHC.

Figure 1.1: Overall view of the LHC. View of the 4 LHC detectors: ALICE, ATLAS, CMS and LHCb [5].

the LHC and the four largest experiments at the LHC. The LHC is part of the extensive accelerator infrastructure at CERN and directly supercedes the Super Proton Synchrotron (SPS). The LHC is a superconducting and symmetric proton-proton collider, accelerating and colliding protons in four different interaction regions with a design center-of-mass energy of 14 TeV at a design collision frequency of 40 MHz. At the four interaction points the four large LHC experiments are located: The two general purpose experiments ATLAS [6] and CMS [7], the heavy-ion focused ALICE [8] experiment and LHCb [9], focused on b-physics and measurements of CP violation.

The LHC has been in operation since the end of 2009, albeit with a reduced center-of-mass energy of 7 TeV at first. In this time data collected at the LHC has contributed significantly to research efforts concerning the standard model of particle physics. The most famous discovery at the LHC so far is without doubt the discovery of the Higgs boson by both ATLAS and CMS in 2012, a particle predicted in 1964.

A key figure to quantify the performance of a collider like the LHC is the *instantaneous* luminosity  $\mathcal{L}$ . Together with the cross section of interest  $\sigma_{\rm exp}$  the total number of events  $N_{\rm exp}$  is given as

$$N_{\rm exp} = \sigma_{\rm exp} \cdot \int \mathcal{L}(t) dt.$$

(1.1)

Today's particle accelerators accelerate beams of bunched particles instead of continuous beams. Each of these particle bunches contains a number  $N_p$  of particles and a number  $n_b$  of bunches form each of the colliding beams. Using a form factor F to describe the transverse beam profiles and incident angles in the collision point and the collision frequency f, it holds

for the instantaneous luminosity

$$\mathcal{L} \propto \frac{N_p^2 n_b f}{4\pi F},\tag{1.2}$$

assuming  $N_{p,1} = N_{p,2} = N_P$ . For the LHC the design peak luminosity is given as  $10^{34} \text{cm}^{-2} \text{ s}^{-1}$  at a center-of-mass energy of 14 TeV. Both the ATLAS and CMS detectors are designed to be able to cope with this luminosity for the expected life span of the LHC of approximately 15 years, until 2025. This time span includes several long shutdown periods spanning from the months long end-of-year shutdowns to longer maintenance works. The amount of proton-proton collisions in this time-frame is usually not given as an absolute number of collisions but instead expressed in terms of the *integrated luminosity*  $\mathcal{L}_{int} = \int \mathcal{L} dt$  in units of inverse barn<sup>3</sup>. As of 2020, the LHC has delivered a total integrated luminosity of approximately 190 fb<sup>-1</sup> over its first two runs combined. Until the end of life of the LHC an additional 260 fb<sup>-1</sup> are expected to be delivered at the LHC design center-of-mass energy of 14 TeV [10].

With rare processes and events having exceedingly small cross sections such a large number of collisions is necessary to allow any precision measurements and significant discoveries in particle physics. As an example, the total production cross section for the Higgs boson from proton-proton collisions is roughly 60 pb [11]. Following Equation 1.1 in the first two runs of the LHC only roughly  $1.1 \cdot 10^7$  collisions involving Higgs bosons have been produced at the LHC. For actual data analysis only a small subset of these collisions is available however, as the acceptance and efficiency of the detector as well as the different production- and decay-channels have to be taken into consideration. As a statistical process, the error of any measurement conducted with a particle detector scales with the number of observed events as

$$\sigma_{\rm stat} \propto \frac{1}{\sqrt{N_{\rm Event}}},$$

(1.3)

and thus halves if the amount of data is quadrupled. Consequently for rare processes, a very large number of proton-proton collisions is necessary to achieve sufficient sensitivity. For investigations of possible beyond-standard-model physics with an even smaller cross section, even more collisions are necessary.

## 1.1.1 The High-Luminosity LHC

With the current luminosity a significant decrease in statistical errors at the LHC is not feasible with several years of runtime only yielding marginal improvements. Additionally especially the inner parts of the ATLAS and CMS detectors will quickly exceed their radiation

$<sup>^{3}</sup>$  1 b = 100 fm<sup>2</sup>

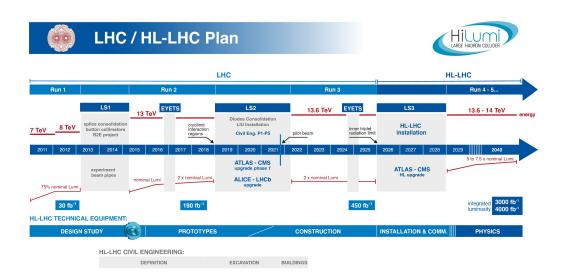

Figure 1.2: Project schedule for the HL-LHC taken from [10]. The upgrade to the HL-LHC will take place starting around 2026, as of January 2022.

tolerance, reducing the detection efficiency by a large margin.

In order to address this, the LHC will be upgraded to the High Luminosity Large Hadron Collider (HL-LHC) after the third run period starting in 2022 [10], increasing the instantaneous luminosity by a factor of up to 7.5 to roughly

$$\mathcal{L} \le 10^{35} \text{cm}^{-2} \,\text{s}^{-1}. \tag{1.4}$$

Such an upgrade requires a major overhaul of the LHC infrastructure, including new superconducting magnets, accelerating cavities and novel technologies to further increase the luminosity in the interaction region. Research and development efforts for the accelerator upgrade have been progressing in parallel to the physics program during the past years. In Figure 1.2 an overview of the LHC schedule, including past physics runs, the accelerator upgrade progress and the future HL-LHC runs, are shown. The HL-LHC upgrade will allow the LHC to remain at the forefront of particle physics for the next decades.

# 1.2 The ATLAS Experiment

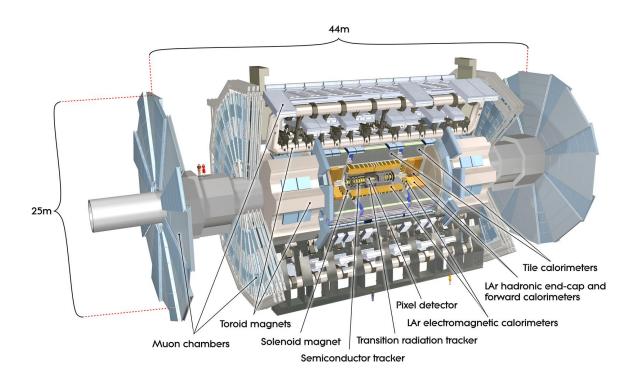

With a length of 45 m and a diameter of 25 m the ATLAS experiment is the largest particle detector built to this day. It is one of the general purpose particle detectors at the LHC aimed

Figure 1.3: Computer generated image of the whole ATLAS detector. Two people are shown true to scale as a reference [12].

at finding as many different physics signatures as possible. A computer generated image of the ATLAS detector is shown in Figure 1.3. The ATLAS detector utilizes a large range of different particle detection techniques in different sub-detectors. These sub-detectors are deployed in multiple layers around the interaction region and can be categorized as barrel sections surrounding the beam pipe and disk layers perpendicular to the beam pipe, see also Figure 1.3. Functionally the ATLAS detector can be categorized in three different groups, starting from the interaction region.

Closest to the beam pipe is the inner detector, the ATLAS Inner Detector (ID), enclosed by a solenoid magnet system, which generates a 2 T magnetic field inside the ID volume parallel to the beam pipe. This magnet field allows the measurement of particle momentum based on track curvature for charged particles. The ID further measures particle trajectories, or tracks. With the primary and secondary interaction vertices being reconstructed from these tracks, the ID contributes significantly to event reconstruction in ATLAS.

Following the ID are the calorimeters in the ATLAS detector. The calorimeters consist of alternating and layers of absorber material and active detector layers. In the absorber layer, cascades of secondary particles, known as showers, are generated from the energy deposited

in the absorber from an incident particle. The active detector layer measures these secondary particles and their energy. Depending on the choice of absorber material and thickness, the calorimeter can be specialised for the detection of certain particles. In ATLAS, the innermost calorimeter is the Electromagnetic Calorimeter, which measures the energy of light charged particles and photons. It is followed by the Hadronic Calorimeter, which measures the energy of hadrons. Both the Electromagnetic Calorimeter and Hadronic Calorimeter are segmented to provide coarse spatial resolution. The calorimeters furthermore allow determination of the missing transverse energy,  $E_T$ , in a recorded event.  $E_T$  is a crucial quantity in a hadron collider, as only the initial transverse momentum in a collision of partons is known. This allows for the reconstruction of particles otherwise invisible for the detector, e.g. neutrinos.

Being a high-mass but not strongly interacting particle, the muon can traverse the inner layers of the ATLAS detector with most of its energy left. The unique combination of heavy mass, long lifetime and no strong interaction gives the muon a unique signature which allows the selection of events of interest for physics analyses. Therefore an additional detector layer is deployed at the outermost part of the ATLAS detector dedicated to measure traversing muons, the Muon Spectrometer. This detector consists of several layers of barrel and disc segments. In addition to the measurement of muon tracks, the momentum is measured by means of the track curvature in a toroidal magnet field surrounding the Muon Spectrometer. Depending on the location of the detector the bending field strength varies between  $1.5 \le X \le 5.5 \,\mathrm{T}$  m in the barrel region of the spectrometer and  $1 \le X \le 7.5 \,\mathrm{T}$  m in the disc region.

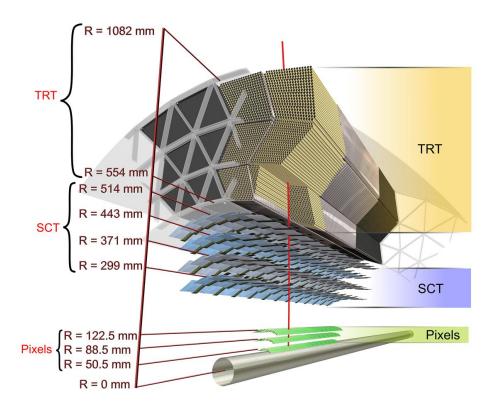

#### 1.2.1 The ATLAS Inner Detector

The ATLAS ID consists of three subsystems. Closest to the beam pipe is the pixel detector, with the innermost layer of the pixel detector, the Insertable B-Layer (IBL), being directly attached on the beam pipe [13]. It is followed by a silicon strip detector, the SCT. The outermost part of the ID is the transition radiation tracker TRT consisting of O(100) straw planes in both barrel and end-caps. A computer generated image of the original ID is shown in Figure 1.4.

The original ATLAS pixel detector consisted of three layers of pixels in both barrel and end-caps. In a major upgrade in 2013, an additional layer was introduced, the IBL [13]. Each of these layers consists of hybrid pixel detectors which offer excellent accuracy and can cope with the environment found close to the interaction region in terms of radiation tolerance and occupancy. The high granularity and performance of pixel detector comes at significant cost in both complexity, material introduced into the detector and resources required to assemble the detector.

The SCT, following the ATLAS pixel detector, consists of 4 double-sided layers of silicon strip detectors. As a strip detector, the SCT sacrifices segmentation in one dimension, thus

Figure 1.4: Computer generated schematic view of the original ATLAS ID without the IBL. Additionally shown in red is a charged track of  $10 \text{ GeV } p_T$  traversing the ID [14].

resolution, in favour of reduced complexity, detector material and cost. With an active area of approximately 61 m<sup>2</sup>, the SCT is a pragmatic and cost-efficient choice compared to an extended pixel detector. Being much further away from the interaction region than the pixel detector, the requirements in terms of radiation - and occupancy tolerance for the SCT are much more relaxed compared to ATLAS pixel.

The TRT is a straw tube detector. This gaseous detector consists of more than 300 000 drift tubes 4 mm in diameter and approximately 1.5 m long. The space between the straw tubes is filled with gas with significantly different refractive index, promoting the generation of transition radiation, giving the TRT its name. The TRT enables effectively continuous tracking by providing a large number of measurement points per tracks, 36 on average, compared to 4 points in the pixel and strip detectors respectively. It provides a cost-efficient solution to cover the outer part of the ID at the cost of slightly reduced resolution and a

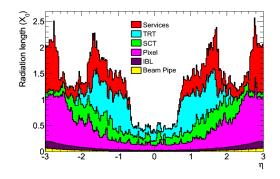

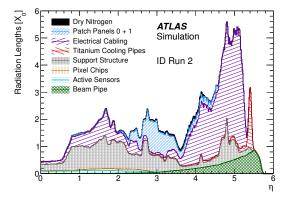

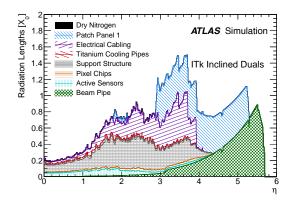

- (a) Material budget of the full ATLAS ID.

- (b) Material budget of the full ATLAS ID pixel.

Figure 1.5: Radiation length as a function of  $\eta$  for the different ID components as implemented in the ATLAS geometry model. Shown are the overall ID in Figure 1.5(a) and the pixel system in Figure 1.5(b) [13].

significantly lower tolerance to pile-up.

In Figure 1.5(a) the total material budget of the ATLAS ID including IBL is shown. Only contributions inside the detection volume are included, services and material outside the TRT is not shown. As can be seen the services of the ID provide the largest contribution to the detector material especially in the forward regions with larger  $\eta$ . As the services are obviously passive material in the detector they negatively impair the performance of the ID. It is thus especially important for the pixel detector to minimize the material budget, as the pixel detector offers the highest granularity on its own. In Figure 1.5(b) the material budget is shown for the pixel detector including IBL. In the forward region with approximately  $|\eta| > 1.5$  the services dominate the material budget of the ATLAS pixel detector.

### 1.2.2 The ATLAS Phase 2 Upgrade and the ITk Project

The HL-LHC upgrade introduced in Section 1.1.1 provides two main challenges for detectors like the ATLAS detector, which are most pronounced in the inner part of the detector:

- An increase in integrated luminosity  $\mathcal{L}_{int}$  corresponds to an increase in radiation dose received by the detector over the time of life.

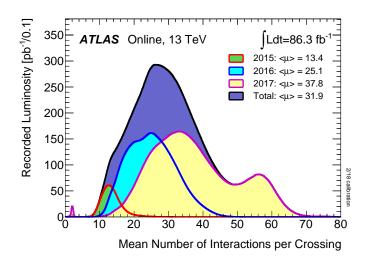

- The increased instantaneous luminosity \( \mathcal{L}\) leads to more interactions per bunch crossing, leading to higher occupancy in the detector. In Figure 1.6 the increase of particle interactions per bunch crossing in the ATLAS detector is shown over the last years. Each of these interactions results in several particles traversing the ATLAS detector. In the HL-LHC approximately 200 primary interactions are expected per bunch crossing.

Figure 1.6: Luminosity-weighted distribution of the mean number of interactions per bunch crossing for proton-proton collisions at 13 TeV recorded between 2015 and 2018. [15].

For the inner detectors to be able to cope with such an increase in occupancy a higher granularity of the detector and larger data bandwidth is needed.

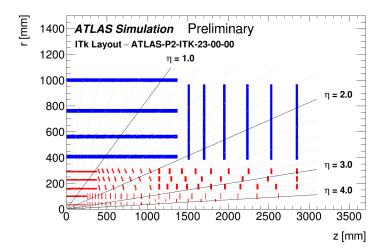

The current ATLAS ID is not able to cope with the requirements imposed by the HL-LHC. Especially the gaseous TRT is expected to be saturated at an instantaneous luminosity  $\mathcal{L} < 5 \cdot 10^{34} \text{cm}^{-2} \, \text{s}^{-1}$ . Instead the new tracking detector will be an all silicon tracker, consisting of pixels and strips. Simply expanding on the already installed pixel and SCT is not an option, as the currently installed hybrid pixel and microstrip detectors in the ATLAS ID will reach the limit of their capabilities by the end of Run 3. The requirements in terms of radiation hardness and rate capabilities can not be fulfilled by the currently employed detector technology. It is thus necessary to design a completely new inner detector with novel hybrid pixel and microstrip detectors. The new detector is referred to as the ATLAS ITk. A schematic layout of the ITk is shown in Figure 1.7.

In the current baseline layout the ITk consists of 5 layers of pixel modules and 4 layers of strip modules. The total dimensions of the ITk is constrained to the dimensions of the ATLAS ID: approximately 6 m in length with a radius of just below 1.1 m. To improve the physics performance, the ITk covers a larger range in the forward region up to  $\eta < 4$  compared to  $\eta < 2.5$  in the ATLAS ID. This results in an increase of the active area, resulting in approximately  $200 \, \mathrm{m}^2$  of active silicon area and more than 5 billion readout channels. The work presented in this thesis was conducted in the context of the ATLAS ITk pixel project.

In the ITk pixel detector different types of modules will be used to address the different challenges imposed by the HL-LHC. The detector will consist exclusively of hybrid pixel

Figure 1.7: The schematic depiction of the ITk Layout, including the updated layout for the Pixel detector. Only one quadrant and only active detector elements are shown. The active elements of the strip detector are shown in blue, and those of the pixel detector are shown in red. The horizontal axis is along the beam line with zero being the interaction point. The vertical axis is the radius measured from the interaction region [16].

detector modules, see also Section 2.2. The majority of these modules will be quad chip modules, four readout chips, abbreviated as readout chip (ROC), bump bonded to a single sensor. In the innermost layer triplets of three single chip modules on a triplet flex printed circuit board (PCB) will be used. The modules in the innermost layer will utilize 3D sensors, which offer an increased radiation hardness and reduced power consumption. In the outer layers, planar sensors will be used, which are less radiation hard but easier to manufacture and more cost efficient. The complete inner system (IS) of the ITk pixel detector is designed to be replaceable after approximately half the time of life of HL-LHC. This is necessary as the projected radiation dose received after the full life time of HL-LHC exceeds the capabilities of any currently known detector technology. To reduce the pile-up in the ITk pixel detector, the granularity of the detector is increased. Compared to pixel sizes found in the ATLAS ID ranging between  $50 \times 400 \,\mu\text{m}^2$  and  $50 \times 250 \,\mu\text{m}^2$ , the pixel size in the ITk pixel detector will be reduced to  $50 \times 50 \,\mu\text{m}^2$  and  $25 \times 100 \,\mu\text{m}^2$ . The increased granularity and size of the pixel detector leads to a significantly larger power consumption of the full detector. A conventional parallel powering scheme as employed in the ATLAS ID pixel detector is simply impossible due to the spatial constraints in ITk. As a low-mass and power efficient alternative a Serial Powering serial powering (SP) scheme will be used for the ITk pixel detector, see Chapter 3. In Table 1.1 a comparison of key parameters of the ATLAS ID pixel detector + IBL to the future ITk pixel detector is given.

|                  | ATLAS Pixel + IBL                                                       | ITk Pixel                      |

|------------------|-------------------------------------------------------------------------|--------------------------------|

| Modules          | 2000                                                                    | 8500                           |

| Pixel Size       | $50 \times 400  \mu\text{m}^2 \text{ or } 50 \times 250  \mu\text{m}^2$ | $50 \times 50  \mu \text{m}^2$ |

| Readout channels | 80 million                                                              | 5 billion                      |

| Active area      | $1.7\mathrm{m}^2$                                                       | $14\mathrm{m}^2$               |

| TID              | 2.5 MGy                                                                 | 10 MGy                         |

| Fluence          | $10^{15}  \mathrm{n_{eq}/cm}$                                           | $1.4^{16}  n_{eq}/cm$          |

| Trigger rate     | 100 kHz                                                                 | 1 MHz                          |

| FE data rate     | 160 Mb s                                                                | 5.12 Gb s                      |

| Powering         | parallel                                                                | serial                         |

| Cooling budget   | 15 kW                                                                   | 100 kW                         |

Table 1.1: Comparing the current ATLAS Pixel detector including IBL with the future ITk Pixel detector.

# Silicon Pixel Detectors in High Energy Physics

Silicon is one of the most abundant and - for modern civilization - most important elements on earth. As a semiconductor it plays a crucial role in the modern electronics industry, which relies heavily on semiconductor devices to be able to fabricate integrated circuits and microelectronics. In a tracking detector like the ATLAS ITk, silicon is used both for the readout ASIC as well as the active detector volume - the sensor.

A tracking detector needs to provide sufficient spatial resolution, which is accomplished by segmenting the detector. Based on the layout of this segmentation, silicon tracking detectors can be differentiated as silicon strip detectors and silicon pixel detectors. Silicon strip detectors offer high granularity in one direction compared to silicon pixel detectors, which are finely segmented in two dimensions. Silicon strip detectors thus trade resolution and thus tracking performance for simplicity and lower cost. In a large tracking detector like ATLAS ITk with some  $200\,\mathrm{m}^2$  active silicon surface, such a compromise is a necessity. Thanks to constant advances in the semiconductor industry, most importantly modern complementary metal-oxide-semiconductor (CMOS) processes with small feature sizes, pitches of a few  $\mu$ m between pixels or strips can be achieved.

Modern ASIC are fabricated on wafers, thin disks of crystalline silicon, which serve as the substrate for the later ASIC. From these wafers, typically 200 mm - 300 mm in diameter, the ASIC are cut after all undergoing several microfabrication process steps, e.gdoping, etching and photolithographic patterning. The resulting dies are typically only a few cm<sup>2</sup> in size. In the context of silicon pixel detectors, the pixel module is built from such dies. The module represents the most fundamental building block in a pixel detector.

#### 2.1 Silicon Particle Detectors

Silicon particle detectors operate by reading out the electric signal due to the energy loss of an incident particle in the sensor volume. Such an incident particle, depending on the particle type and its energy, deposits energy in the silicon bulk, refer to Section 2.1.1. The active silicon sensor volume typically consists of a depleted space-charge region at the junction between p-doped and n-doped silicon. The energy deposited in the silicon generates free charge carriers, which immediately recombine with the silicon lattice, unless generated in the depletion region. Charge carriers freed in the depletion region instead drift in the electric field across the p-n-junction. This drift generates a signal in the readout electrodes connected to the sensor. Since the charge generated is proportional to the energy deposited in the sensor, the energy of incident particles can be measured with silicon detectors as well, provided they deplete all their energy in the active volume.

#### 2.1.1 Particle Interaction with Matter

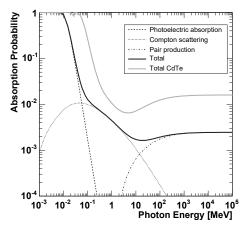

The interaction of particles with matter depends on the particle type and energy. For photons the dominant effects are the photoelectric effect, Compton scattering and pair production at high energies. In Figure 2.1(a) the resulting total absorption probability for photons in 300 µm silicon is shown. The photon is completely absorbed should it undergo pair production or be absorbed via the photoelectric effect. When interacting via Compton scattering the photon is instead scattered at a large angle. Consequently, the photon is completely absorbed with a certain probability when traversing through e.g. a silicon sensor.

Charged particles however continuously deposit energy in the detector material instead of being stopped immediately. Energy can be deposited in multiple ways, e.g.

- inelastic scattering with shell electrons,

- elastic scattering with atomic nuclei,

- radiation losses, e.g. bremsstrahlung, transition radiation or Cherenkov radiation,

- nuclear reactions.

The mean energy loss due to ionization per distance in an absorber material is described by the Bethe-Bloch equation [11]:

$$-\left\langle\frac{\mathrm{d}E}{\mathrm{d}x}\right\rangle = K\frac{Z}{A}\varrho\frac{z^2}{\beta^2}\left[\frac{1}{2}\ln\frac{2m_ec_0^2(\beta\gamma)^2T_{\mathrm{max}}}{I^2} - \beta^2 - \frac{\delta(\beta\gamma)}{2}\right],\tag{2.1}$$

with

- $K = 4\pi N_A r_e^2 m_e c_0^2 = 0.307 \,\text{MeV} \,\text{cm}^2 \,\text{mol}^{-1}$ ,  $c_0$  the speed of light in vacuum,  $m_e$  and  $r_e$  the electron mass and the classical electron radius,

- Z, A being the atomic number and nucleon number of the absorber material,  $\varrho$  the density of the absorber,

- z the charge of the incident particle,

- the Lorentz factors  $\beta = \frac{v}{c_0}$  and  $\gamma = \frac{1}{\sqrt{1-\beta^2}}$  describing the incident particle,

- the maximum energy transfer in a head-on collision  $T_{\rm max} \approx 2 m_e c_0^2 (\beta \gamma)^2$ ,

- the Fermi density correction  $\frac{\delta(\beta\gamma)}{2}$  important for incident particles with high energy.

- the material density  $\rho$  and the mean excitation energy I of the absorber material

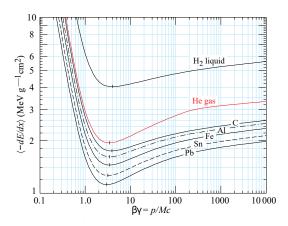

The Bethe-Bloch equation gives a good approximation of the energy loss, or stopping power, for incident particle energies  $0.1 \le \beta \gamma \le 1000$  with an accuracy of a few percent in different absorbers [11]. In Figure 2.1(a) the energy loss according to Equation 2.1 is shown for different absorber materials. For low particle energies with  $\beta \gamma \le 1$  the energy loss is strongly dependant on the initial energy. The energy loss reaches a local minimum around  $\beta \gamma \approx 3$ . For particle energies  $3 \le \beta \gamma \le 1000$  the mean energy loss only increases moderately. Thus particles with  $\beta \gamma \ge 3$  are commonly referred to as minimum ionizing particles, or MIPs. In silicon the energy loss of a MIP can be approximated [17] as

$$-\left\langle \frac{\mathrm{d}E}{\mathrm{d}x} \right\rangle_{\mathrm{MIP Si}} \approx 3.87 \,\mathrm{MeV \, cm}^{-1}. \tag{2.2}$$

For high energetic particles energy losses due to bremsstrahlung and other radiation effects become dominant. This is especially relevant for light leptons such as electrons, positrons and muons. Bremsstrahlung is not described by the Bethe-Bloch equation, as is the interaction of indistinguishable particles. Thus Bethe-Bloch does not describe the stopping power for electrons, which is dominated by bremsstrahlung. Energy loss by bremsstrahlung is proportional to the energy of the particle:

$$-\left(\frac{\mathrm{d}E}{\mathrm{d}x}\right)_{\mathrm{brems}} = \frac{E}{X_0},\tag{2.3}$$

with the radiation length  $X_0$  [17]. The radiation length is the mean path length in an absorber after which the incident particle's energy  $E_0$  has been to reduced to  $E = \frac{1}{e}E_0$ .  $X_0$  is a material

- (a) Probability of photon absorption for  $300\,\mu m$  silicon as function of the photon energy. Contributions from different processes are indicated [18, p. 34].

- (b) Mean energy loss rate of ionizing particles in matter as a function of relativistic energy  $\beta \gamma$  as from Equation 2.1. Modified from [11, p. 537].

Figure 2.1: Absorption probability and energy loss rate for different particle types and energy in matter.

property of the absorber. In a mixture or compound of different materials, the total radiation length is approximated by

$$\frac{1}{X_0} = \sum \frac{\omega_j}{X_i},\tag{2.4}$$

where  $X_j$  is the radiation length and  $w_j$  the fraction by weight of the j-th compound [11, p. 541]. In silicon the radiation length is approximately  $X_{0,\mathrm{Si}} \approx 9.36\,\mathrm{cm}$  [17, p. 65]. The radiation length is a common unit of measurement of the material budget of components in a particle detector.

#### 2.1.2 Signal Generation and Detection

In a typical silicon pixel detector the active volume is the depletion region at the junction between p-doped and n-doped silicon. Considering as an example a typical n-in-p-type planar sensor, a weakly doped p-type silicon is chosen as the bulk material. The readout electrodes are implemented as segmented, highly doped n-silicon. Due to the different doping concentration in p-type and n-type silicon, when applying a reverse bias voltage, the depletion region at the p-n-junction can grow several  $100 \, \mu m$  into the p-type bulk, effectively filling the full bulk of the sensor. In this example, the n-doped electrodes are kept at ground potential and the negative bias voltage is applied to the sensor backside. The sensor backside does not need to be segmented and only requires a metal interface to connect to the bias voltage.

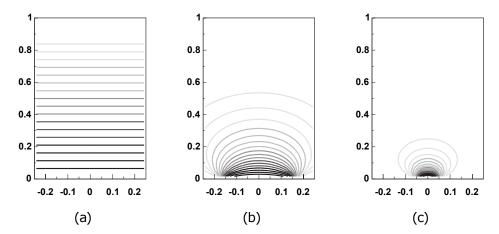

Incident particles generate free charge carriers in the depletion region by exciting electrons from the valence band to the conduction band. This way two charge carriers are created: an free electron in the conduction band and a defect electron or hole in the valence band. The

Figure 2.2: Weighting potential between two parallel electrodes of varying width on the X-axis, compared to the vertical bulk thickness on the Y-axis. The electrodes in (a) are of infinite size, 1/3 of the distance between the electrodes in (b) and 1/10 of the distance between the electrodes in (c) [18, p. 61].

average number of electron-hole pairs generated at room temperature is given by

$$N_e - h = \frac{E}{\omega},\tag{2.5}$$

with the deposited energy E and the mean energy  $\omega$  required to create an electron-hole pair. For silicon  $\omega \approx 3.65$  eV [17].

The electric field present in the depletion region causes these charges to drift apart. The signal in the readout electrode is dominated by the current induced from the movement of charges in this electric field according to the Shockley-Ramo theorem [19]. The induced current is given as

$$i = e\vec{E}_{\rm W}\vec{v},\tag{2.6}$$

with the charge carrier charge e, velocity  $\vec{v}$  and the weighting field  $\vec{E}_{\rm W}$  [17, p. 135]. The weighting field for different electrode sizes is shown in Figure 2.2. For infinitely large electrodes a moving charge carrier will induce the same signal in the readout electrode for any part of its drift path. For small electrodes only charges drifting close to the electrode contribute meaningfully to the signal read out. In a pixel detector with several neighbouring readout electrodes the weighting fields of each electrode overlap. A charge created in one pixel cell can thus also induce a signal in neighbouring pixel in an effect referred to as charge sharing.

The silicon pixel sensor itself is typically characterized by its diode-like IV curve. The most important figures are the leakage current and the breakdown voltage. The leakage current is the amount of current flowing through the sensor as a function of the reverse bias voltage

applied. As the reverse bias voltage of a sensor is increased, the depletion zone in the sensor volume grows and the leakage current increases slightly. This increase in leakage current saturates once the sensor volume is fully depleted until the reverse bias voltage exceeds the breakdown voltage of the sensor, at which point the leakage current increases drastically. Such a breakdown can lead to irreversible damage to the sensor and is thus to be avoided. The breakdown voltage is strongly influenced by the sensor design. The pixel sensors used in the ITk pixel detector will utilize either planar sensors or 3D sensors. These sensor types have different internal structures, with the planar sensor having its readout electrodes parallel to the sensor surface, thus planar, and the 3D sensor electrodes being perpendicular to the sensor surface. 3D sensors offer a much increased radiation hardness due to the reduced drift length in the sensor, however are much more expensive to produce. Additionally breakdown occurs much quicker for 3D sensors compared to planar sensors, which needs to be considered in the design of the ITk pixel detector.

#### 2.1.3 Spatial Resolution

A pixel detector with binary read out, i.e. no charge information is available, has a spatial resolution according to [17, p. 843]

$$\sigma_i = \frac{a_i}{\sqrt{12}},\tag{2.7}$$

with  $a_i$  referring to the pixel pitch and  $\sigma_i$  to the resolution in x or y direction. For small pixels the charge signal can be registered by several neighbouring pixels. This leads to clusters in the hit data. If charge information is available the center of gravity of the cluster can be used as the mean hit position. This significantly improves on the spatial resolution. The spatial resolution when considering charge sharing follows as

$$\left(\frac{\sigma_i}{a_i}\right) = \frac{1}{2\pi^2} \sum_{m=0}^{\infty} \frac{1}{m^2} \cdot e^{-4\pi^2 m^2 \left(\frac{\sigma}{a}\right)^2},\tag{2.8}$$

assuming gauss shaped signal distribution at the readout electrodes and neglecting noise.  $\frac{\sigma}{a}$  denotes the width of the gaussian charge distribution in units of the width of the readout electrode. Assuming a gaussian charge distribution a near perfect reconstruction can be obtained for  $\sigma \geq \frac{a}{2}$ . In the limit of small signals  $\frac{\sigma}{a} \to 0$ , Equation 2.8 simplifies to Equation 2.7 [17, p. 844].

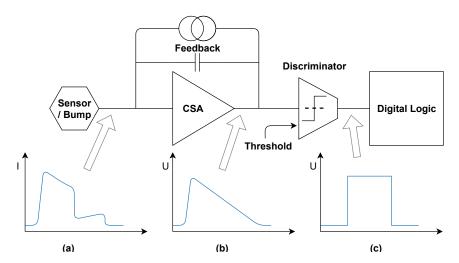

Figure 2.3: Generic pixel detector front-end electronic circuit. The signal shape is depicted as a current pulse coming from the sensor (a), the voltage pulse generated by the charge sensitive amplifier (CSA) in (b) and the discriminator output in (c). Taken from [20].

#### 2.1.4 Signal Processing

The charge signal induced on the readout electrodes requires further processing and digitization. This is typically achieved by the analog front-end electronics (AFE) of a pixel detector as shown in Figure 2.3. The charge collection electrode of each sensor pixel is connected to the input node on the left hand side. Usually each sensor pixel is connected to its own dedicated readout electronics. The input signal is a charge pulse induced on the readout electrode of the sensor pixel as shown in Figure 2.3 (a). The first stage in the typical signal processing chain is a CSA, which converts the induced charge pulse into a voltage pulse by integrating the input signal. The amplitude of the CSA output signal is proportional to the integrated charge, while the slope of the falling edge depends on the feedback current. When using a constant current feedback as is done here, the falling edge of the CSA is linear as shown in Figure 2.3 (b). With a sufficiently steep rising edge, the width of the CSA output signal is thus proportional to the integrated charge as well. The CSA can be followed by additional amplification stages to increase the signal gain or shape the signal further.

The output signal of the amplification stage is fed into a discriminator, which compares the CSA output signal to a given threshold voltage. As the signal exceeds this threshold voltage the discriminator switches its output from low to high and vice versa, digitizing the output signal of the CSA. In an ideal case the discriminator output would be described by a step function, corresponding to the signal shown in Figure 2.3 (c). The width of the rectangular output signal of the discriminator corresponds to the duration for which the CSA output is above the threshold voltage of the discriminator and is referred to as time over threshold (ToT). As the width of the CSA output signal is approximately proportional to the input charge, the

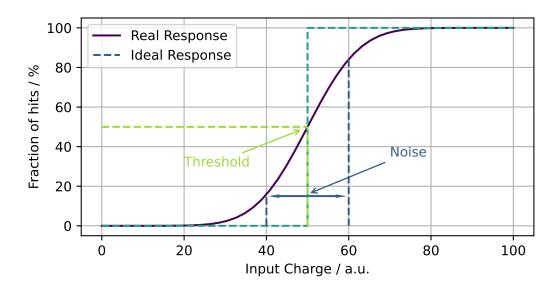

Figure 2.4: Arbitrary S-curve as defined in Equation 2.9. In addition the response of an ideal discriminator is given. The threshold is defined as the input charge for which 50% of hits are recognized. The noise is derived from the width of the S-curve.

ToT is a measure of the energy deposited in the sensor. In the digital logic of the front-end the ToT is counted in units of clock cycles.

Due to electrical noise the response function of a discriminator does not follow an ideal step function but instead is described using the error function as [17, p. 753]

$$P_{\rm hit}(Q_{\rm in}) = 1 - {\rm erf}\left(\frac{Q_{\rm in} - \mu}{\sigma\sqrt{2}}\right).$$

(2.9)

Here,  $P_{\rm hit}(Q_{\rm in})$  denotes the probability for a given charge Q to result in a high discriminator output level.  $\mu$  is the threshold of the discriminator and  $\sigma$  denotes the noise. The resulting S-curve is shown in Figure 2.4. The threshold of the discriminator is then defined as the input charge  $Q_{\rm in}$ , for which the probability of the discriminator output being high is 50 %. The noise contribution to the signal processing can be extracted from the width of the S-curve. Assuming gaussian distributed noise the relevant reference points for the width of the S-curve are  $P_{\rm hit}(Q_1) = 16$  % and  $P_{\rm hit}(Q_2) = 84$  %. The resulting width corresponds to 1  $\sigma$  of the full noise.

## 2.2 Hybrid Pixel Detector Modules

In high energy physics applications silicon pixel detectors are the detectors of choice for the innermost layers of tracking detectors at particle colliders due to their excellent spatial and timing resolution. In addition pixel detectors can cope with the harsh environment present in the interaction points of particle colliders like the LHC. The pixel system in a detector like ATLAS plays a fundamental role in particle identification and reconstruction of primary and secondary vertices. The basic building block of the pixel system is the pixel module. For pixel modules two general design approaches can be used. Combining the active sensor and the readout electronics in the same silicon bulk yields a pixel module classified as a Monolithic Active Pixel Sensor, or MAPS. Alternatively the readout electronics and active volume can be realized in two independent silicon dies, which are then interconnected to form a hybrid pixel module. Both approaches have their inherent advantages and disadvantages [21]. In the ATLAS ID as well as the future ATLAS ITk hybrid pixel modules are used exclusively.

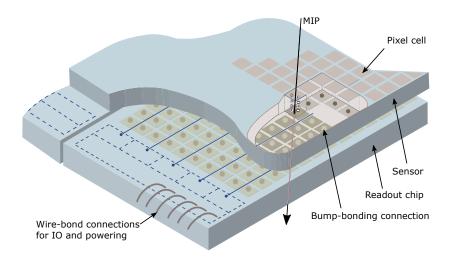

#### 2.2.1 Modules

The hybrid pixel detector module traditionally consist of a silicon sensor connected to one or more readout chips using a flip chip process. Modern pixel detectors provide significant challenges for this flip chip process due to the very small pixel pitch and the large amounts of pixels per ASIC. While the high-density bump bonding process is a very expensive and error prone process, the hybrid pixel module offers significant advantages as the readout chip and sensor can be designed and optimized individually. A schematic view of a hybrid pixel module is shown in Figure 2.5. Here, the pixelated readout chip is on the bottom and bump-bonded to the sensor tile on the top. Typically the bump bonds are deposited on either the sensor tile or the readout chip before the sensor is placed on top of the readout chip face-down, thus flip chip. After necessary alignment the stack of sensor and readout chips is heated up until the bump bonds melt and form an electrical and mechanical connection between both chips. Wire bonding pads on the readout chip periphery, which is not covered by the sensor, provide connectivity to the services of the pixel detector.

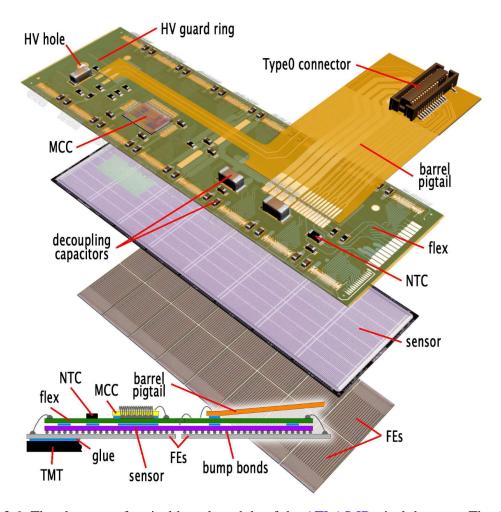

Connection of the hybrid pixel module to the detector services, including power, data and control signals, is done using high density interconnect circuits, typically on a flexible PCB or module flex. Figure 2.6 shows the full module stack for a barrel module of the current ATLAS pixel detector.

The sensor in this ATLAS pixel module features 47232 pixels arranged in 144 columns and 328 rows for a total active surface of  $6.08 \times 1.64 \text{cm}^2$ . Connected to this sensor are 16 readout chips with 2880 pixel cells each [23]. Glued to the sensor backside is the module flex, an approximately 100  $\mu$ m thin PCB to route signals and power. Bias voltage for the sensor is

Figure 2.5: Schematic view of a hybrid pixel detector with square pixels. A MIP is shown to traverse through a single sensor pixel. Wire bond connections of the readout electronics are shown. Modified from [22].

applied via a dedicated hole in the sensor. Depending on the location of the pixel module, the module flex is directly connected to the Type-0 services or connected via an additional thin foil, called pigtail [23]. The material budget of a barrel layer pixel modules used in the ATLAS detector and perpendicular to the incident particle is  $1.2 \% X_0$ , to which the different components contribute [24]:

• sensor:  $0.32 \% X_0$ ,

• bump bonds and readout chip:  $0.27 \% X_0$ ,

• flex hybrid:  $0.39 \% X_0$ ,

• pigtail:  $0.22 \% X_0$ .

#### 2.2.2 Services

The high granularity of a pixel detector directly translates into the need for a large amount of cables to service the detector in terms of power supply, data acquisition (DAQ) and control signals. This makes the services one of the most significant contributors to the overall material budget of a pixel tracking detector, see also Figure 1.5(b). Especially in the forward region, where cables leave the detector volume, the contribution from services to the material budget far exceeds the contribution from the actual detector. This degrades the performance of all following subdetectors in this region. Additionally such a large concentration of cables can make routing difficult as only limited space is available.

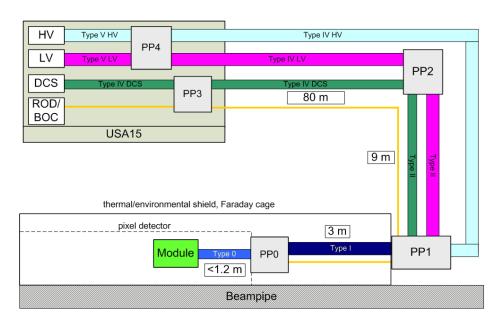

Figure 2.6: The elements of a pixel barrel module of the ATLAS ID pixel detector. The thermal management tile on which the module is glued is suppressed [23].

To mitigate these difficulties the services for the ATLAS pixel detector use a modular design as shown in Figure 2.7. The services can be disconnected at intermediate locations between the detector and the services cavern using patch panels. There are a total of 4 patch panels. Readout chip power low voltage (LV) and sensor bias voltage high voltage (HV) are routed from the power supplies to PP4. The HV is directly routed to PP1 via the Type IV HV cables. The LV is routed via Type IV, PP2 and Type II cables to PP1. From PP1 power is supplied to the module via the Type I and Type 0 services with the intermediate PP0. The Type 0 services connect directly to the module flex. Data transmission is done electrically from the module to PP0, as the high radiation levels do not allow optical data transmission. Initially from PP0 data is transmitted optically to the service room [25]. However due to radiation damage to the electro-optical converters, the conversion to optical signals now takes place in a better serviceable location outside the ID volume [26].

Figure 2.7: Simplified schematic view of the layout of the services for the ATLAS ID pixel detector [25].

Of these services a dominant fraction by mass is contributed by the LV cables. The ATLAS pixel detector with its millions of readout channels has a current consumption of approximately 3.7 kA [6, p. 82]. In traditional powering schemes as used for ATLAS pixel, power is either supplied directly from the power supply to the module in a direct or independent powering scheme or alternatively multiple modules are connected in parallel to a common LV line. Such powering schemes allow a high level of control over the pixel detector, as even single modules can be powered off at will. However with the large amount of pixel modules in a detector like ATLAS pixel, they introduce a large amount of material into the detector. To mitigate the contribution of these LV cables to the material budget of the detector, cables with a small cross section can be chosen. Of course depending on the cable material and the cross section A of the cables, a current dependent voltage drop V

$$A = l \cdot \frac{I}{V} \cdot \frac{1}{\sigma} \tag{2.10}$$

occurs with the current flow I and the conductivity of the cable  $\sigma$ . Minimizing A thus leads to an increase in V, as the total cable resistance increases. This increases the power losses on the cables  $P = V \cdot I$ . Not only does this reduce the power efficiency of the system, costing money, but also this power dissipation generates heat which needs to be removed, requiring massive cooling plants. For safety reasons, the voltage drop V on the cables is constrained to prevent possible over voltages on the modules. As a result the LV cable cross section can not be minimized and presents major contributions to the services material budget and

effectively fills the cable channels in the detector. In the current ATLAS pixel detector the total services dominate the total pixel material budget. The Type 0 services in particular account for approximately  $0.13 \% X_0$  split between [24]

• LV cables:  $0.10 \% X_0$ ,

• HV cables:  $0.02 \% X_0$ ,

• data transmission:  $0.01 \% X_0$ .

The future ITk pixel detector with its larger size, more modules and readout channels as well as higher power consumption per module due to the increased granularity will only make this issue more pressing. A traditional approach as used in ATLAS pixel will simply not be possible anymore and a new, efficient powering scheme needs to be employed.

# Serial Powering - A Novel Powering Scheme for the ITk Pixel Detector

In the current ATLAS pixel detector, a large contribution of the total material budget consists of detector services especially in the forward direction as shown in Section 1.2.1. Of these services, the power cables are the most significant contributor, as each detector module is powered by an independent set of cables. In order to minimize the material budget, the power cable diameter needs to be as small as possible. As a smaller diameter results in a larger cable resistance and thus increased power loss, the achievable cable dimensions are limited by the available cooling budget and acceptable detector power efficiency. During initial operation of the current ATLAS pixel detector, the power efficiency was expected to be as low as 25 %. For a total power consumption of 6 kW in the readout chips, a total of 24 kW had to be provided to the detector to account for the power losses in the services, totalling to 18 kW [6].

In the ITk pixel detector the per module current consumption per active area was expected to increase by a factor 2 to 4 with respect to IBL modules in order to meet the requirements set for a pixel detector in the HL-LHC environment, especially the increased granularity. Using the same cables as in the current ATLAS pixel detector the power efficiency would drop below 10 %. Since the new ITk pixel detector will be significantly larger as well, more cables are needed to service the detector, which results in more inactive material inside the detector volume. While the low power efficiency is already undesirable, the increased material inside the ITk would be unacceptable from a physics performance view. Ultimately, a different low-mass, high-efficiency powering scheme is required to service the future ITk pixel detector.

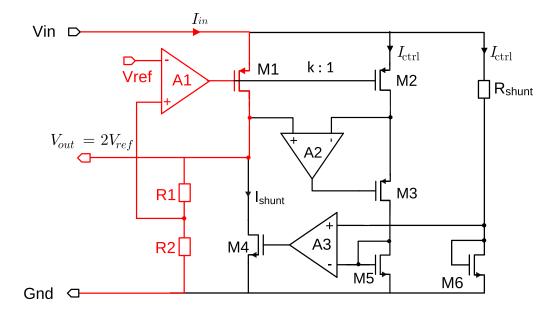

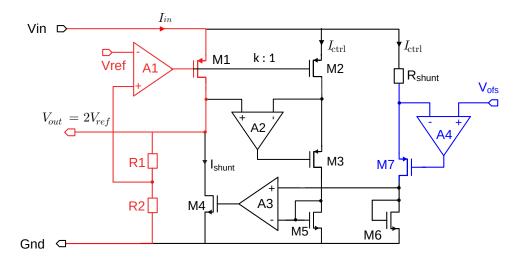

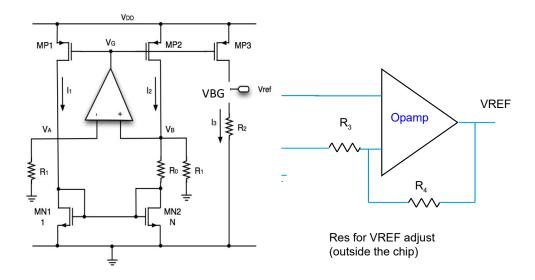

The two most promising candidates are DC-DC conversion and Serial Powering serial powering (SP) [27–29]. Both ATLAS ITk pixel as well as the future CMS pixel detector have decided to use SP as a baseline powering scheme. The core element of the used SP

schemes will be the Shunt-LDO regulator, a voltage regulator with shunt capabilities designed explicitly for use in a serially powered pixel detector.

As SP is a completely novel powering scheme for large scale pixel detectors, it requires a significant amount of prototyping to verify design choices for ITk. These efforts range from component prototyping, as for example the different iterations of the Shunt-LDO circuitry outlined in Chapter 4, to large scale prototyping like the Outer Barrel Demonstrator (OBD) in Chapter 5.1. Such large scale programs are invaluable, as they offer needed insights on system level aspects of SP, which may not be accessible during inital prototyping stages, like chip testing.

# 3.1 Serial Powering Concept

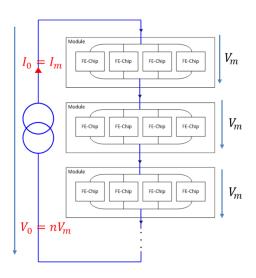

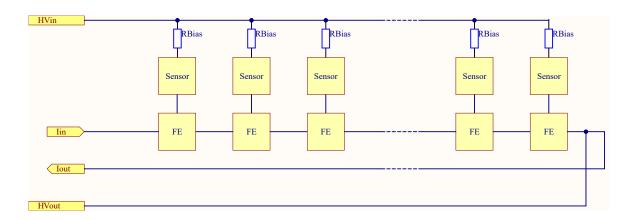

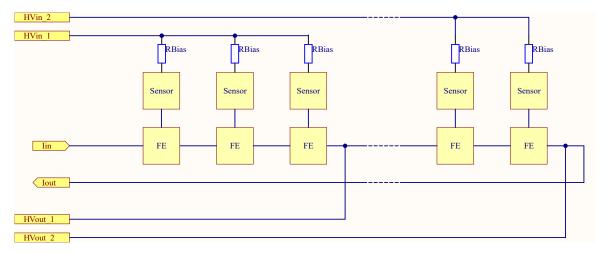

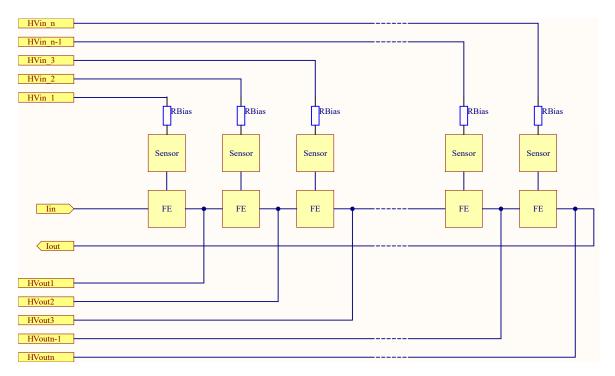

In an SP scheme, a number n of modules is powered in series by a constant current. Within a SP chain, the local ground of each module is the input potential of the following module. In the following the *first* module in a serial powering chain refers to the module with the highest local ground potential, while the last module in the serial chain has the lowest local ground potential, typically the same as the system ground. A sketch of a SP chain can be seen in Figure 3.1. Here, every module consists of four readout chips connected in parallel to provide redundancy in case of failure of a single chip. The required current  $I_0$ for the SP chain is defined by the module with the largest current draw. Naively assuming a constant current draw for each module, the voltage drop  $V_{\rm m}$  would remain unchanged compared to parallel powering. With the additional assumption of the

Figure 3.1: Simplified serial powering scheme consisting of quad-chip pixel modules.

same type of cable being used such that the power loss on each individual cable  $P_{\text{Cable}}$  is constant, the power dissipation for an SP chain of length n would be

$$\begin{split} P_{Module} &= V_{\rm m} \cdot I_0, \\ P_{Cable} &= R_{\rm Cable} \cdot I_0^2, \\ P_{Chain} &= n \cdot P_{\rm Module} + P_{\rm Cable}, \end{split}$$

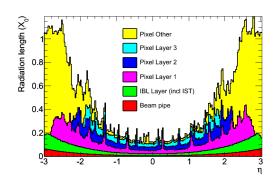

- (a) Radiation length  $X_0$  versus the pseudorapidity  $\eta$  for the current ATLAS ID pixel detector [30].

- (b) Radiation length  $X_0$  versus the pseudorapidity  $\eta$  for the ITk pixel detector [16].

Figure 3.2: Simulated material budget of the current ATLAS pixel detector during Run 2 (a) and the ITk (b). Contributions from different components are shown. The figures only show positive  $\eta$ ; negative  $\eta$  is expected to look the same. The serially powered ITk pixel detector shows a significantly lower material budget, especially in the forward region.

compared to a parallel powering scheme consisting of n modules

$$P_{\text{Parallel}} = n \cdot (P_{\text{Module}} + P_{\text{Cable}}).$$

A comparison of such key figures in serial and parallel powering schemes can also be seen in Table 3.1. It can be seen that, depending on the contribution of the detector services to the total power budget, an SP scheme can offer a significant increase in power efficiency. At the same time SP can bring a significant reduction in the material budget used in the detector. Figure 3.2 shows a comparison of the simulated material budget of the current pixel detector during Run 2 data taking and the future ITk, as proposed in [30]. The overall material budget of serially powered ITk is significantly smaller, especially in the forward region, where the cables leave the detector alongside the beam pipe. Using a conventional parallel powering scheme, the material budget especially in the forward direction would be unacceptable. Additionally the required cables would not fit in the volume available for services in ITk pixel.

The approach does not consider the fact that a pixel readout chip actually behaves more akin to a variable ohmic load instead of a resistor. For a SP scheme to operate reliably the pixel modules need to display the electric characteristic of an ohmic resistor instead. In order to address this, the supply voltage for each readout chip is generated by dedicated voltage regulators on the module. As the powering scheme is based on a constant current supply which needs to cover the maximum possible current draw, there is always an excess current

| Parallel and serial powering of <i>n</i> modules |             |                          |             |                 |                                                              |  |

|--------------------------------------------------|-------------|--------------------------|-------------|-----------------|--------------------------------------------------------------|--|

| Scheme                                           | Total mod-  | PSU                      | Cable cross | Power loss      | Powering effi-                                               |  |

|                                                  | ule current | voltage                  | section     |                 | ciency                                                       |  |

| Parallel                                         | $n \cdot I$ | $V_{ m Mod}$             | A           | $R \cdot I^2$   | $\frac{V \cdot I}{V_{\text{Mod}} \cdot I + R \cdot I^2}$     |  |

| Serial                                           | I           | $n \cdot V_{\text{Mod}}$ | A/n         | $R \cdot I^2/n$ | $\frac{V \cdot I}{V_{\text{Mod}} \cdot I + R \cdot I^2 / n}$ |  |

Table 3.1: Key figures of parallel and serial powering schemes with n modules being powered. Compared are the total current input in the system I, the power supply (PSU) terminal voltage V, the voltage drop over a pixel module  $V_{\text{Mod}}$ , the cable cross section A, which is inversely proportional to the cable resistance R, needed to service the modules, power losses on the cables and the powering efficiency. In an SP scheme, the reduced power losses on cables lead to a significant improvement in power efficiency.

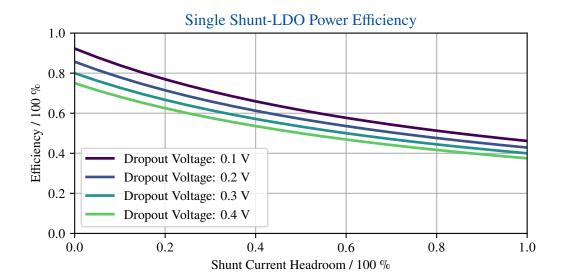

that needs to be shunted. A constant current supply is used opposed to a constant voltage supply, as it is inherently more resistant to load transients: with a high output inductance, a constant current supply has a high transient impedance. Thus in the case of fast load changes, e.g. if a chip in the serial chain fails, the output current of the power supply remains very stable [31]. Both objectives are covered by the Shunt-LDO, see also Section 3.2, a voltage regulator specifically designed for serially powered pixel detectors. Although the inherent current draw of these regulators is almost negligible, they increase the average power consumption of the pixel modules. This is caused by an additional voltage drop in the Shunt-LDO, the dropout voltage  $V_{do}$ . For a typical Shunt-LDO as will be discussed in this work,  $V_{\rm do}$  is typically in the order of 300 mV. As can be seen from Figure 3.6 and Equation 3.13, this additional voltage drop reduces the power efficiency of a single regulator by O(20%) on its own. This provides a non negligible challenge for the design of the local supports of the ITk pixel detector, as the power dissipation of the pixel modules is increased significantly and requires a more potent cooling system. Ultimately the saved material budget in an SP scheme and the significantly reduced total power consumption of the system more than compensate for this added inefficiency.

However the serial connection of pixel modules brings additional risks and challenges at the system level, which are not present in parallel powering.

Within each SP chain, all modules are on different local ground potentials, which makes AC-coupling of all data links mandatory, see Section 3.1.1. The varying ground potentials in a SP chain also need to be considered for the HV distribution, see Section 3.1.2, scheme. With the HV leakage current  $I_{\text{leak}}$  being returned via the LV line, the HV must be distributed in a way that does not short the serial powering chain.

Noise can propagate on the power lines, adversely affecting the full serial chain unless

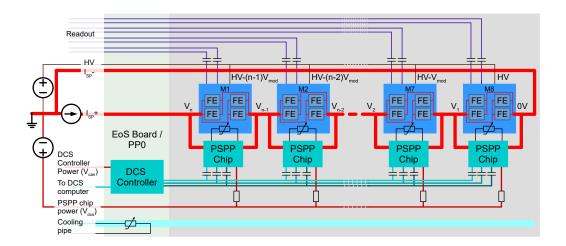

filtered properly, e.g. within the Shunt-LDO. Should a module in an SP chain fail high ohmic, thus interrupting the chain, the full chain would be put out of operation. Such a failure may be the result from a malfunction on the ROC or on the services. Similarly, no individual module can be switched on or off. Some of these risks can be mitigated by redundancy on the module level. Should the readout chip fail electrically open, the chain current can be shunted by the Shunt-LDO. Each readout chip is equipped with two separate Shunt-LDO regulators connected in parallel. This allows fine tuning of the Shunt-LDO to the current consumption of the analog and digital domains of the ROC, which generally require different supply currents. In principle using two Shunt-LDO per ROC also allows e.g. the digital domain to be operated at a lower core voltage than the analog domain, as is the case in the FE-I4, and provides some redundancy against failure of a single Shunt-LDO. In addition the majority of ITk Pixel module will consist of 4 ROC connected in parallel, such that 8 parallel Shunt-LDO distribute the chain current on module level. If a Shunt-LDO fails on such a module, the remaining Shunt-LDO can take over the additional current, keeping the serial chain operational. This capability comes at the cost of an increased power dissipation in such a faulty module. If too many regulators fail on a single module, the full chain needs to be switched off. Thus the average number n of modules in a serial powering chain is a trade-off between reliability of the detector system and the efficiency of longer serial chains. In a real detector like ITk pixel the feasible length of a serial powering chain is additionally constrained by the layout of the local supports and monitoring systems. In the ITk pixel detector there will be 912 serial powering chains between 3 and 14 modules in length with an average length of 9 modules.

Another set of risks to be addressed are potential overvoltages in a serial chain. These can for example occur if a module fails low ohmic and the PSU can not regulate its output voltage fast enough. If the resulting transients are too large, meaning they exceed the voltage capabilities of the Shunt-LDO or ROC, they can destroy some of the remaining modules in the chain. These can be mitigated, for example, by an active element like the Pixel Serial Powering Protection (PSPP) or a passive, fast voltage clamp to provide overvoltage protection. A different valid approach would be to target the causes and prevent over voltages from occurring in the first place, as it is done in the latest generation of Shunt-LDO, see also Section 4.3.

# 3.1.1 AC-Coupling of Data Signals

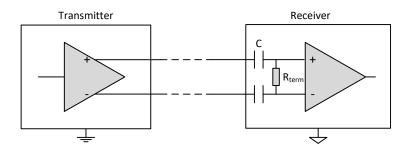

In a serial powering chain, all modules have their own local ground potential  $LV_{\rm out}$ . Only the last module in a chain shares the same ground as the serial powering chain itself, which is also used for the PSU and the readout system. The ROC receives its clock (CLK) and command (CMD) signals from the DAQ, while sending output data to the DAQ. This communication

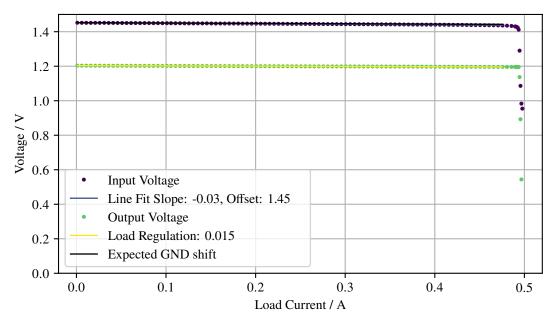

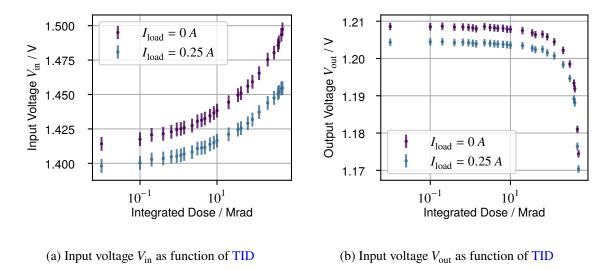

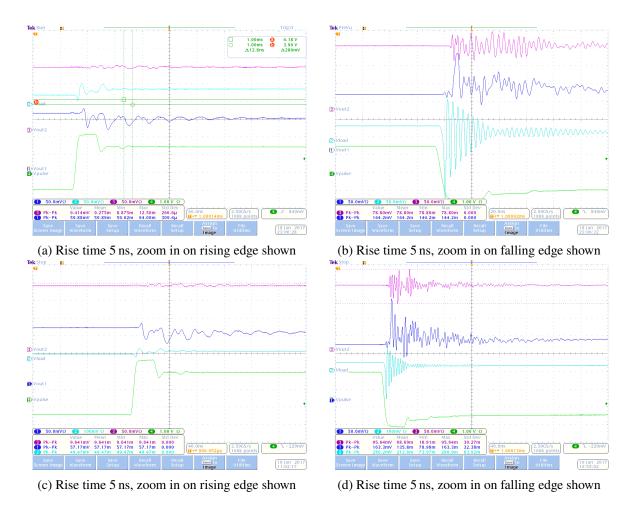

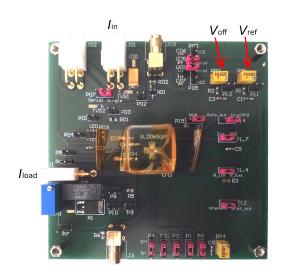

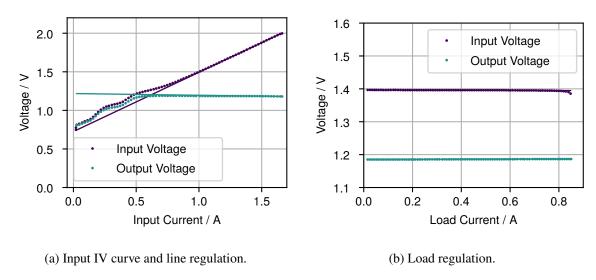

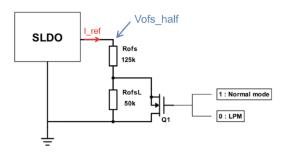

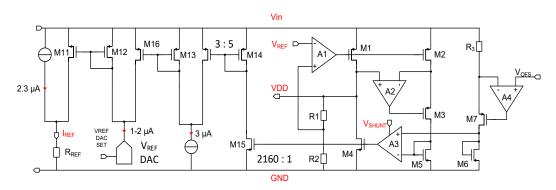

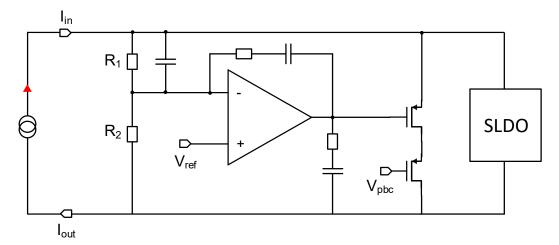

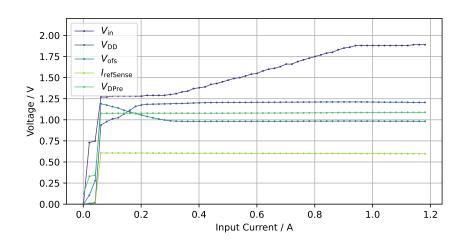

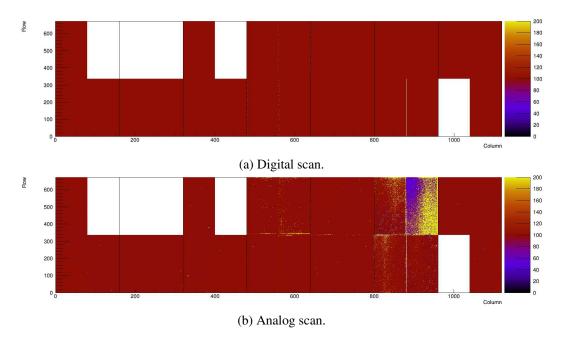

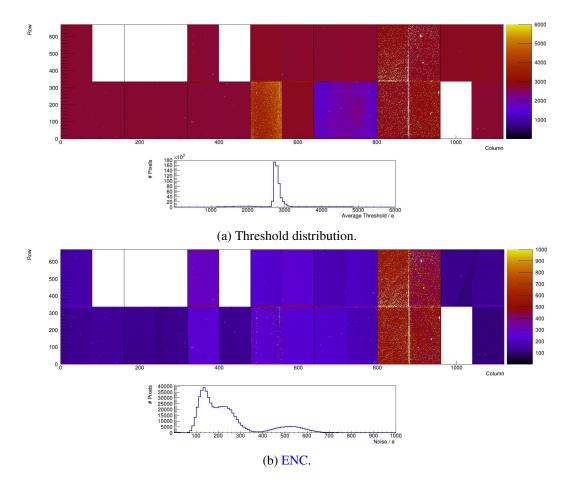

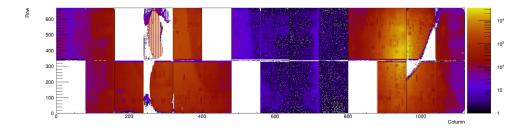

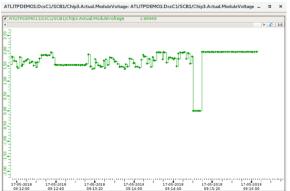

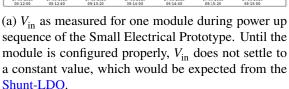

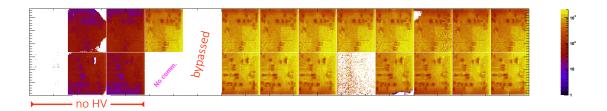

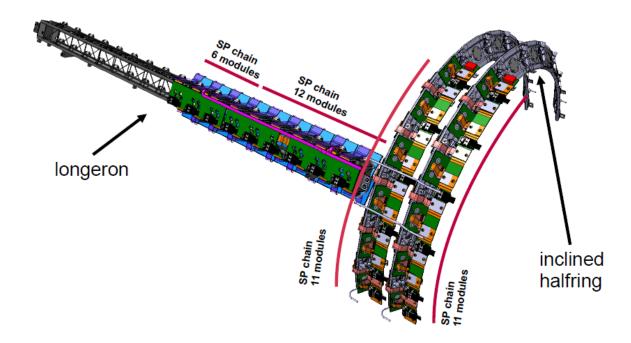

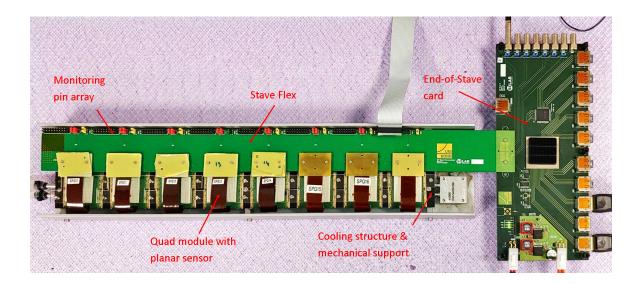

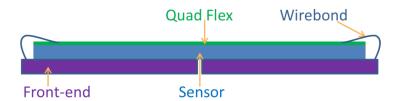

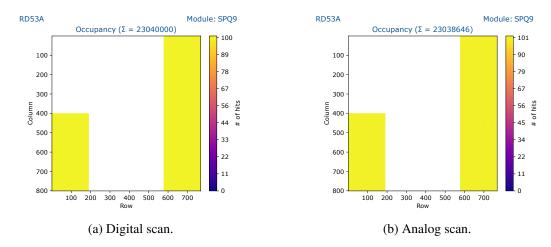

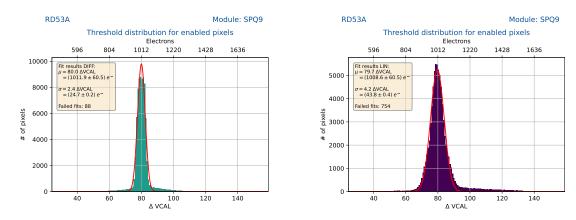

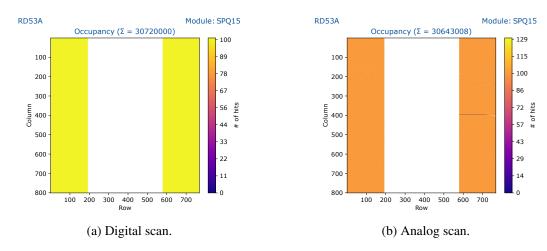

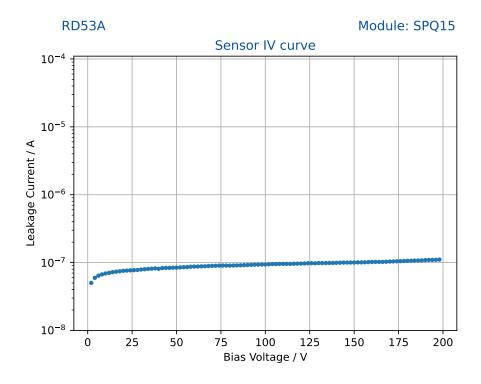

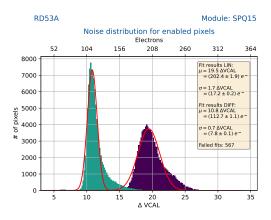

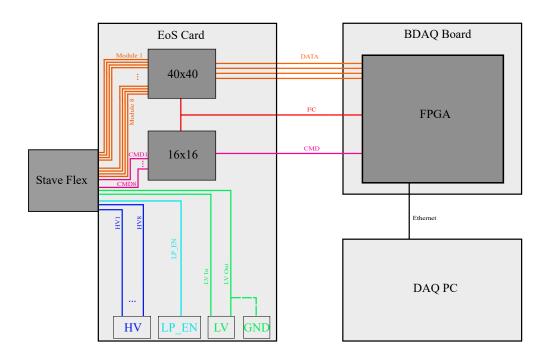

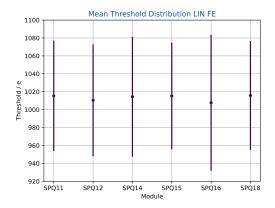

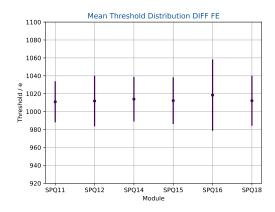

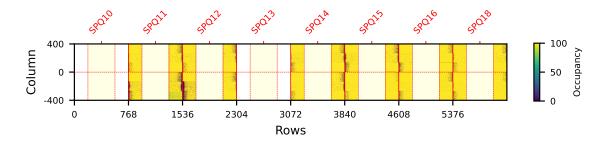

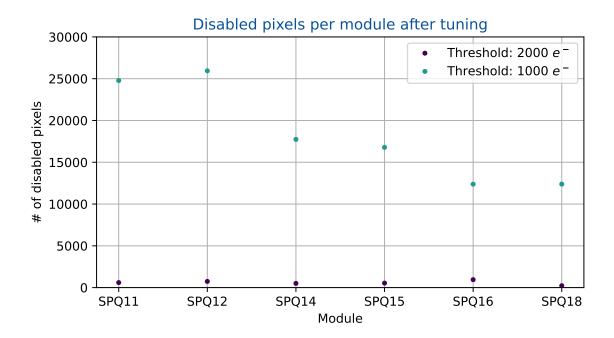

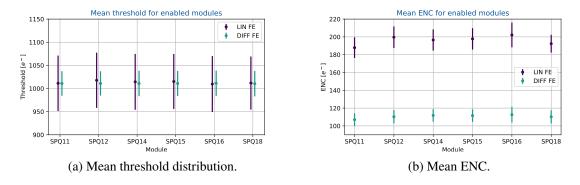

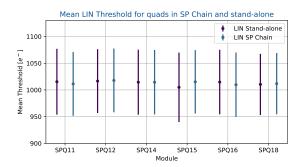

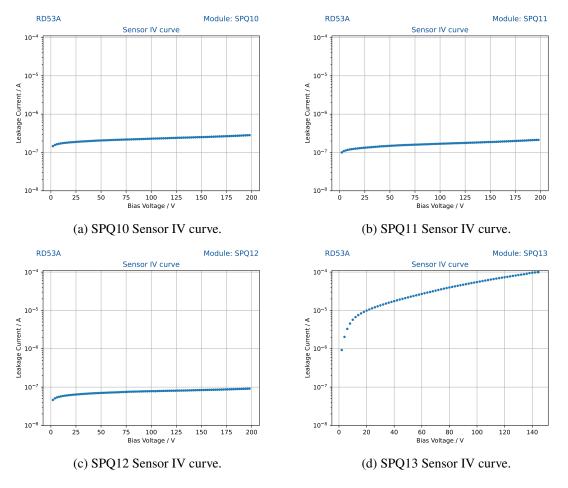

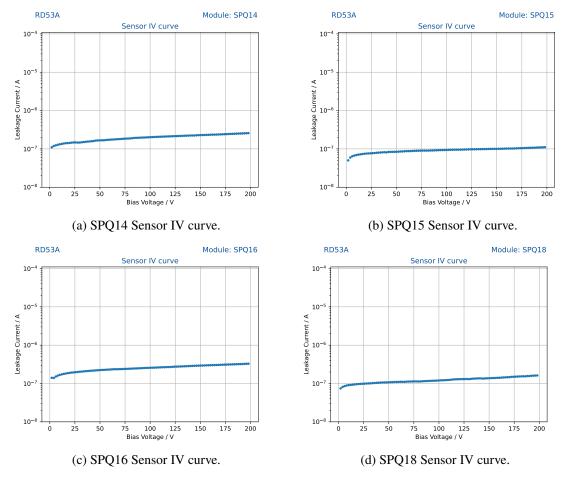

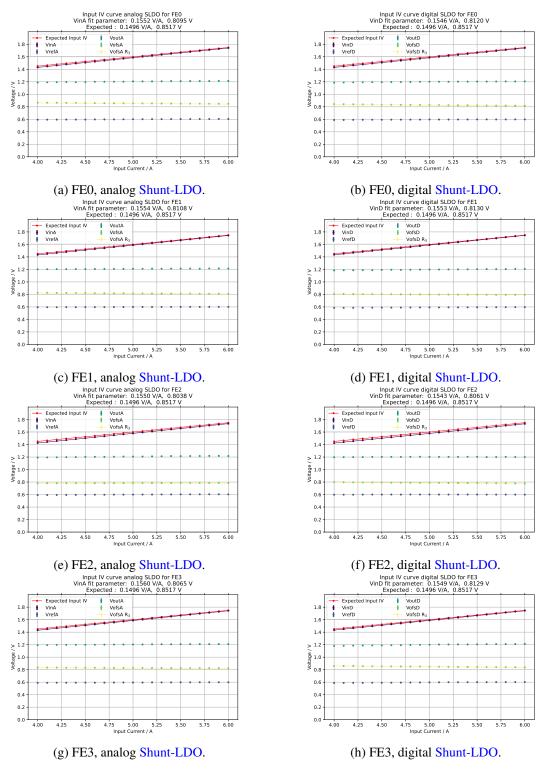

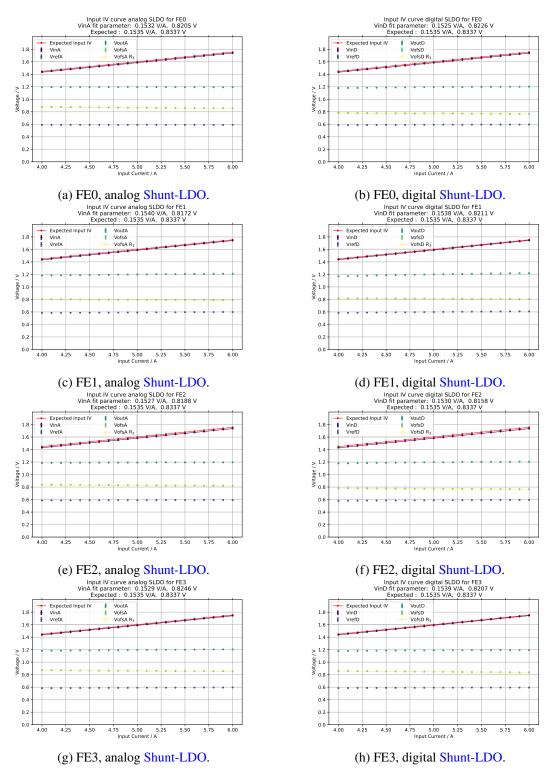

Figure 3.3: Simplified schematic of AC-coupled low voltage differential signaling (LVDS) data links. Capacitors are placed in series on both lines of the differential pair prior to the termination resistor. These filter any DC component in the LVDS signal, which is necessary, as transmitter and receiver in a serially powered detector usually have different ground potentials [24].