# ROUTING BASED PORT ASSIGNMENT AND BUFFERING

DISSERTATION

ZUR

ERLANGUNG DES DOKTORGRADES (DR. RER. NAT.)

DER

MATHEMATISCH-NATURWISSENSCHAFTLICHEN FAKULTÄT

DER

RHEINISCHEN FRIEDRICH-WILHELMUS-UNIVERSITÄT BONN

VORGELEGT VON

FINE FOOS

AUS

DÜSSELDORF

BONN, FEBRUAR 2025

Angefertigt mit Genehmigung der Mathematisch-Naturwissenschaftlichen Fakultät der

Rheinischen Friedrich-Wilhelms-Universität Bonn

Gutachter/Betreuer: Prof. Dr. Stephan Held

Gutachter: Prof. Dr. Jens Vygen

Tag der Promotion: 14. April 2025

Erscheinungsjahr: 2026

## Acknowledgments

During my work on this thesis, I was supported by many people. First of all I want to thank my supervisor Prof. Dr. Stephan Held for the support, contributed ideas and in-depth feedback to the thesis. I enjoyed collaborating in the development of PANGEA REUSE. I would also like to thank Prof. Dr. Dr. h.c. Bernhard Korte, Prof. Dr. Jens Vygen and the entire professorial staff of the Institute for Discrete Mathematics for creating a great place to work and think. I will miss the Arithmeum.

My joy in this work came from both the great people and the interesting projects. So I would like to thank all my current and former colleagues for being excellent coworkers. Special thanks go to Dr. Siad Daboul for supervising my work as a student, to Dr. Pietro Saccardi for leaving me the beautiful code of BONNPANGEA (and chip-scenario), and to Susanne Armbruster for being the best office partner I could have hoped for. Thank you to everyone organizing and participating in our institute's cocktail pong events, especially to those who lost and then brought cake.

Big thanks also go to everyone who helped me proofread preliminary versions of this thesis: Susanne Armbruster, Paula Heinz, Ragni Hinderling, Luise Puhlmann and my mother.

I would also like to thank several IBM employees for the great collaboration regarding BONNPANGEA and helping me test BONNROUTEBUFFER: Bill Dougherty, Greg Klos, Genevieve Shafer and Jesse Surprise.

Thank you to my family for supporting me throughout my studies and of course all the years before.

Lastly, I want to thank my partner Svenja Dubendorff. You endured the years of me being away from home (which are finally over!), you support me in everything sensible I do and you gave me the occasional (or less occasional) nudge to actually get up and work. And most importantly: Thank you for bringing a fluffy whirlwind into my life, I did not know what I was missing before.

# Contents

|          |                                                                                    |           |

|----------|------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                                | <b>5</b>  |

| <b>2</b> | <b>Preliminaries</b>                                                               | <b>7</b>  |

| 2.1      | Basic notions of chip design . . . . .                                             | 7         |

| 2.2      | Embedded routing . . . . .                                                         | 8         |

| 2.3      | Applications . . . . .                                                             | 9         |

| 2.3.1    | Pangea . . . . .                                                                   | 9         |

| 2.3.2    | BonnRouteBuffer . . . . .                                                          | 10        |

| 2.4      | Global routing framework . . . . .                                                 | 11        |

| 2.4.1    | Resource sharing algorithm . . . . .                                               | 12        |

| 2.4.2    | Arrival time customers . . . . .                                                   | 13        |

| 2.4.3    | Incorporating further constraints . . . . .                                        | 13        |

| 2.5      | Timing . . . . .                                                                   | 14        |

| 2.5.1    | Elmore delay model . . . . .                                                       | 15        |

| 2.5.2    | Linear delay model . . . . .                                                       | 16        |

| <b>3</b> | <b>Algorithms for timing-constrained global routing</b>                            | <b>17</b> |

| 3.1      | Global routing oracle . . . . .                                                    | 17        |

| 3.1.1    | Topology generation . . . . .                                                      | 17        |

| 3.1.2    | Embedding . . . . .                                                                | 18        |

| 3.2      | Topology algorithms . . . . .                                                      | 19        |

| 3.2.1    | Reachaware topologies . . . . .                                                    | 19        |

| 3.2.2    | Timing-aware topologies . . . . .                                                  | 21        |

| 3.3      | Tighter approximation for the uniform cost-distance Steiner tree problem . . . . . | 23        |

| 3.3.1    | Main theorems . . . . .                                                            | 23        |

| 3.3.2    | The $(1 + \beta)$ -approximation algorithm . . . . .                               | 24        |

| 3.3.3    | Improving the approximation ratio . . . . .                                        | 25        |

| 3.4      | Cost-distance router . . . . .                                                     | 33        |

| 3.4.1    | Iterative matching algorithm . . . . .                                             | 33        |

| 3.4.2    | Practical improvements . . . . .                                                   | 34        |

| <b>4</b> | <b>Pangea</b>                                                                      | <b>37</b> |

| 4.1      | Preliminaries and problem formulation . . . . .                                    | 37        |

| 4.2      | Related work . . . . .                                                             | 41        |

| 4.3      | Pangea topologies in theory . . . . .                                              | 41        |

| 4.4      | Standard pangea flow . . . . .                                                     | 45        |

| 4.4.1    | Continent border blockages . . . . .                                               | 45        |

| 4.4.2    | Global routing . . . . .                                                           | 46        |

| 4.4.3    | Track assignment . . . . .                                                         | 50        |

| 4.4.4    | Port cutting . . . . .                                                             | 51        |

|                     |                                                                    |            |

|---------------------|--------------------------------------------------------------------|------------|

| 4.5                 | Pangea replay . . . . .                                            | 51         |

| 4.5.1               | Trading off replaying ports with other pangea objectives . . . . . | 53         |

| 4.5.2               | Replaying ports as resource . . . . .                              | 54         |

| 4.6                 | Pangea reuse . . . . .                                             | 55         |

| 4.6.1               | Setting and problem formulation . . . . .                          | 56         |

| 4.6.2               | Reuse flow . . . . .                                               | 57         |

| 4.6.3               | Port intervals . . . . .                                           | 58         |

| 4.6.4               | Blockages on the continent border . . . . .                        | 66         |

| 4.6.5               | First routing pass . . . . .                                       | 66         |

| 4.6.6               | Applying continent equivalence . . . . .                           | 67         |

| 4.6.7               | Second routing pass . . . . .                                      | 70         |

| 4.6.8               | Difficult and reuse incompatible input . . . . .                   | 70         |

| 4.6.9               | Alignment of opposite ports . . . . .                              | 77         |

| 4.6.10              | Reusing feed-throughs . . . . .                                    | 86         |

| 4.6.11              | Pangea reuse in practice . . . . .                                 | 89         |

| <b>5</b>            | <b>BonnRouteBuffer</b>                                             | <b>91</b>  |

| 5.1                 | BonnRouteBuffer in resource sharing . . . . .                      | 91         |

| 5.2                 | Dynamic program for buffering . . . . .                            | 92         |

| 5.3                 | Enhancements and fixes . . . . .                                   | 93         |

| 5.3.1               | Slew computation . . . . .                                         | 93         |

| 5.3.2               | Speed ups . . . . .                                                | 95         |

| 5.3.3               | Other improvements . . . . .                                       | 96         |

| 5.4                 | Experimental results . . . . .                                     | 97         |

| 5.4.1               | Wire synthesis flow . . . . .                                      | 97         |

| 5.4.2               | Metrics and instances . . . . .                                    | 98         |

| 5.4.3               | Different slew pessimism values . . . . .                          | 101        |

| 5.4.4               | Previous vs. improved BonnRouteBuffer . . . . .                    | 105        |

| 5.4.5               | BonnRouteBuffer in the IBM flow . . . . .                          | 113        |

| 5.5                 | Future work . . . . .                                              | 114        |

| 5.5.1               | Slew computations . . . . .                                        | 114        |

| 5.5.2               | Fixing electrical violations in ripup-and-reroute . . . . .        | 114        |

| 5.5.3               | Fast buffering of timing-uncritical nets . . . . .                 | 115        |

| <b>Summary</b>      |                                                                    | <b>117</b> |

| <b>Bibliography</b> |                                                                    | <b>119</b> |

# Chapter 1

## Introduction

As computer hardware becomes more complicated and intricate, so become mathematical problems and algorithms used for their design. Modern computer chips contain billions of transistors and the wire length is measured in kilometers. This just gives a glimpse into the scope of *very large scale integrated (VLSI) chip design*, the field of optimizing processor chips used inside supercomputers.

The tasks of chip design range from designing the logical structure and placing components to routing and timing optimization. However, it is not feasible to merely approach these one after the other. Their objectives are heavily intertwined. During most of the physical design flow, the main objectives are placement density, routing congestion, timing and power consumption.

This thesis contains two main topics, port assignment and global buffering, which we examine from a mathematical and a practical point of view.

Port assignment designs the interface between large chip components. It decides where the routing of one component should connect to the routing of a neighboring one. For a general problem formulation allowing multiply instantiated components, we examine the conditions for feasible solutions to exist and present an algorithm to compute such.

In global buffering, we insert many small components (so-called cells) along the wiring in order to reduce signal delays. Due to the physical properties of wiring and cells, this improves signal delay from roughly quadratic down to almost linear in the wire length [Bar+06]. We need to compute Steiner trees minimizing a combination of net length and path length. For this, we present an algorithm approximating an objective function that occurs when buffering a single net.

We cover the tools BONNPANGEA and BONNROUTEBUFFER. These tools compute practical solutions for port assignment and global buffering.

## Main contributions

We present an approximation algorithm for the uniform cost-distance Steiner tree problem (Section 3.3, already published in [FHS23]). This problem arises in the Lagrangian relaxation of global buffering. We achieve an approximation factor of  $< 2.05$ , which improves upon the previously best factor of 2.39 in [KH20]. Given an exact oracle for the Steiner minimum tree problem, our approximation is tight with respect to the lower bound  $C_{SMT}(T \cup \{r\}) + D(T, r, w)$ . This is because the lower bound can deviate from the optimum value by a factor of  $1 + \frac{1}{\sqrt{2}}$ , while we can compute a  $\left(1 + \frac{1}{\sqrt{2}}\right)$ -approximation using the Steiner tree oracle. All previous analyses compare their results against this

lower bound.

We devise the first mathematical problem formulation of the standard pangea problem (Sections 4.1 and 4.3). Here, the goal is to compute a port assignment allowing for short paths, little wiring congestion and short total net length. We also present the first description of BONNPANGEA, the tool used to solve this problem in practice (Section 4.4). We then extend the problem definition to the case of pangea replay. In pangea replay, a partial port assignment is given in the input. It needs to be extended by the computed result. We describe the adapted algorithm to solve this problem as well (Section 4.5).

In Section 4.6, we present a major new contribution called PANGEA REUSE. Here, we compute a port assignment in the presence of multiply instantiated components, an important practical application. The port assignment on equivalent components must coincide. The problem becomes much more difficult compared to traditional port assignment. We formalize the pangea reuse problem and develop two algorithms: A practical algorithm is described in Sections 4.6.2 to 4.6.7. This algorithm was also implemented and integrated into the existing pangea tool as part of this thesis. It works under certain restrictions which are mostly fulfilled in practice. A second algorithm is presented in Section 4.6.9. We can prove that this algorithm solves the pangea reuse problem correctly on instances that are substantially less restricted.

For BONNROUTEBUFFER, we develop a more accurate propagation of slew limits during the dynamic program and a more accurate propagation of slews through the computed repeater tree. We show that these improvements, together with many minor fixes, lead to more efficient global buffering solutions that also contain significantly fewer electrical violations.

This thesis is organized as follows. Chapter 2 introduces general notions of chip design, focusing on routing and timing optimization. Chapter 3 covers algorithms used for timing-constrained global routing. Chapter 4 gives details on pangea. There we present the three different modes of BONNPANGEA, including PANGEA REUSE. Finally, Chapter 5 addresses BONNROUTEBUFFER and showcases how the author of this thesis was able to improve on many aspects of it compared to its previous state (see [Rot17], [Dab21] and [Dab+23]).

# Chapter 2

## Preliminaries

### 2.1 Basic notions of chip design

This section introduces the most important notions used throughout the entire thesis. A *cell* or *gate* is a small physical component made up of a few connected transistors representing a simple logical function such as *AND*, *NOT* or even the identity function. These functions also create more complex logical functions by composition. Cells represent the building blocks of the chip. To connect wiring to them, cells each have several *pins*. For our purposes, we only ever consider the input pins (e.g. one for a *NOT*-function, two or more for an *AND*-function and so on) and the output pin. In addition to the cells' pins, a chip also has *primary input and output pins*, which are placed on the chip itself. They have a coordinate lying inside the *chip area*, which is a rectangle given in  $\mathbb{R}^2$ .

To state which pins need to be connected to which, we use the notion of a *net*. A net is a set of pins containing exactly one *source* which is either an output pin of a cell or a primary input. The rest of the net's pins are called *sinks*. They are either input pins of cells or primary outputs. The set of all nets forms the *netlist*.

When routing a net, the task is to compute wiring connecting all of the net's pins. Wiring can be placed on multiple *routing layers*. On each such layer, wire segments may either go only horizontally or only vertically (in the *preferred direction*), and such horizontal and vertical layers alternate. Wires on adjacent layers can be connected by inserting a *via* in between the layers.

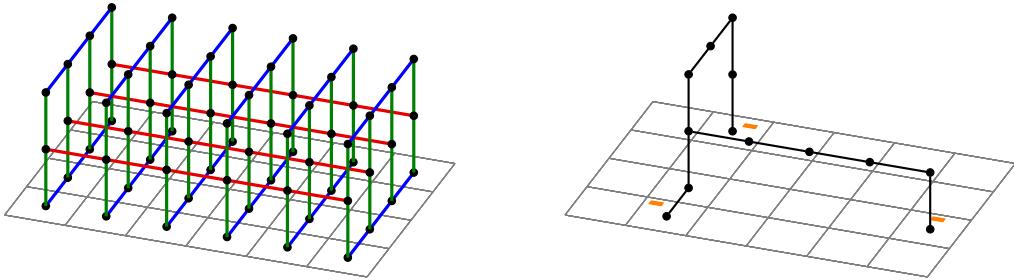

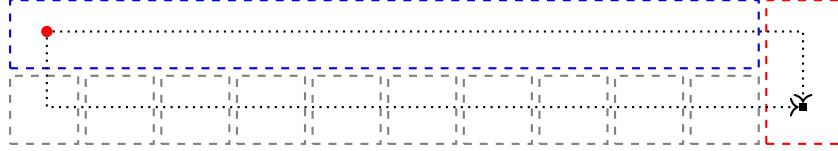

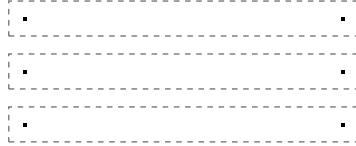

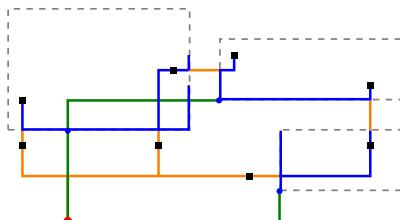

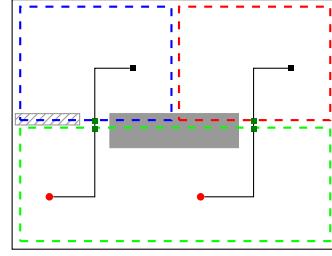

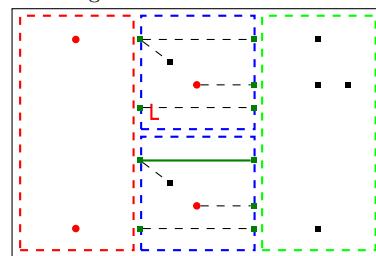

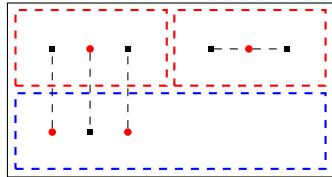

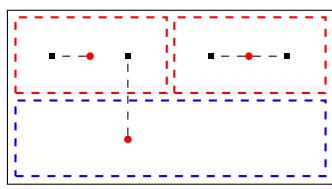

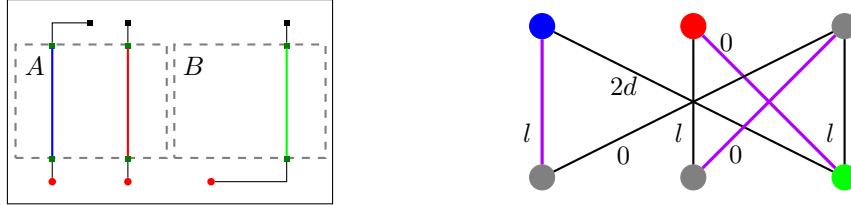

In (global) routing, each layer is cut into tiles forming a grid. The tiles are connected according to their layer's preferred direction. Together with edges representing vias, this forms the *global routing graph*, a 3-dimensional grid graph. Pin positions are projected to the tile-centers of the respective surrounding tiles and each net gets connected via a *global route*, a Steiner tree in that grid graph connecting tile-centers to tile-centers. An example global routing graph and a route are depicted in Figure 2.1.

In some applications, *blockages* will play a role. A blockage is a rectangular shape on either the placement layer or a routing layer. No gates may be placed on a blockage on the placement layer, while no routing (including vias) may be placed intersecting a routing blockage. These blockages can be either user-specified or stem from already placed components not allowed to be changed.

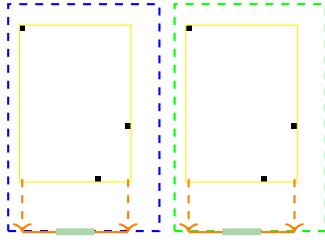

**Figure 2.1:** A global routing graph with three routing layers (left) and a global route for a three terminal net (right). Global routing tiles are depicted by the gray grid. Horizontal, vertical and via routing edges are red, blue and green, respectively. Pins are orange rectangles.

## 2.2 Embedded routing

The core of this thesis is to use a very flexible approach to global routing to be able to tune the computed routes towards certain specific goals.

As the routing task itself is so vast, even when only considering feasibility, it usually gets split into global routing and detailed routing. Global routing places wiring on a rough tile grid and only connects tile-centers to tile-centers (see previous section). It balances density constraints with other objectives. This way, not too much wiring is placed in the same area, the total wire length does not get too large, and single connections are not routed with a too large detour. In contrast, detailed routing places the wires on their exact positions and connects directly to the pin shapes. Additionally, it considers further design rules such as minimum distance constraints between unconnected wire segments. To do this in a feasible running time, detailed routing uses the already computed global routes and follows their structure as closely as possible. Because detailed routing considers each net to be routed one after the other, it also relies on the global routing to have made the decisions which nets should be routed through which areas.

The two most natural objectives in global routing are wire length and congestion. Wire length is the sum of the lengths of all wire segments. This is also called net length. Congestion measures how dense the wiring is. For this, we will use the notion of the wACE4 metric [Wei+14], which is a weighted sum of the routing densities in the 5% densest wiring areas. Depending on the problem at hand, global routing must satisfy other constraints as well. This can include timing constraints, i.e. making sure paths to critical sinks are as straight as possible and route on higher layers, which typically induce less wire delay. Or it can include further structural constraints which we will see in Chapter 4.

Combining a high level view to compute the overall structure of a route with a detailed view for the exact tiles that a single route segment should be placed on is a rather hard problem. These two are separated into individual steps: *Topology generation* and *embedding*. First, we compute a 2-dimensional Steiner tree connecting the source to the sinks. Here, we consider length according to the  $\ell_1$ -metric. We can incorporate many further objectives such as regarding blockages or signal delay. Second, we embed this topology into the global routing graph using a variant of Dijkstra's algorithm [Dij59]. Here, we also decide the wire type on each used global routing edge.

The basis of the used routing engine was already developed in [Hel+18] and extended for the use of BONNROUTEBUFFER by [Dab+23]. Further adaptations, in particular for the use case of pangea, were implemented by the author of this thesis.

## 2.3 Applications

### 2.3.1 Pangea

Before the earth's continents emerged the way they look today, there was a single large continent called *pangea* surrounded by the superocean *panthalassa*. During the early Jurassic era, this continent broke apart into the sections we know today<sup>1</sup>.

Analogous to this process, the pangea flow is used to break apart one large chip into smaller components called *continents*. The goal of this division is to be able to optimize each continent separately instead of having to deal with one very large instance all at once. This drastically speeds up every computational step and allows to exert much more effort in individual optimizations. To make this possible, the pangea flow makes sure the fully optimized continents properly fit together in the final result. This means that for every net with pins inside multiple continents, there has to be an agreement on where the wiring of that net should cross the continent borders. Having fixed these positions, we know the final continents will be compatible, no matter how their interior components and routing will end up looking like.

The decision which areas should make up continents is left to the user. To achieve the aforementioned benefits, it makes sense to choose continents such that their interdependence is rather low. Further, it is advantageous to choose continents of roughly the same size, which will make the optimization of the individual continents more efficient when done in parallel.

A commitment that a net should cross a continent border at a specified position is called a *port*. In addition to its location, every port comes with a predecessor (the net's source or another port) and a set of successors (net sinks or other ports), determining how the net will split into individual nets inside each continent. The ports of a net together with its pins form an arborescence rooted at the source with the set of leaves equal to the set of net sinks. This arborescence is called the *port graph*.

To compute port graphs for all nets, the pangea flow routes all relevant nets and then creates ports at each intersection of a route with a continent border. Of course, having to route or otherwise optimize the entire chip at once is exactly what pangea aims to avoid. To make this task feasible anyway, a number of simplifications are made. The two most important ones are ignoring all nets contained in single continents and using a very large tile size which leads to a comparably small global routing graph (see Section 2.4 for more details). With these simplifications, it is possible to compute a global routing in acceptable time, because both the number of routing tasks and the scope of each task are reduced.

The computed global routes now go from tile-center to tile-center. Placing ports in this state would make no sense, as many ports would end up lying on top of each other. However, to ensure the computed ports can be routed to, they must not overlap at all. As detailed routing would take much too long and is not necessary here to spread out the wiring, track assignment is used instead. One can think of routing tracks as the routing edges in detailed routing. They represent positions where wire segments may be placed next to each other without violating distance requirements. In track assignment, all wire segments crossing a continent border are assigned to such a routing track, ensuring the resulting ports are overlap-free.

For pangea, the key aspect in this flow is the topology generation, the first step in computing a single route. To minimize unwanted effects of fixing certain points of a route beforehand, the number of ports should be kept low. Furthermore, port positions must not enforce large detours in source-to-sink connections of nets. But they need to simultaneously allow for an overall short net length and low congestion. So topology

---

<sup>1</sup><https://www.britannica.com/place/Pangea>

generation has to make sure that

- a) both net length and source-to-sink paths are short and

- b) routes do not switch between continents back and forth too often.

This is achieved by using a hierarchical approach: First, compute how the continents should be connected to each other. Then, how the topology within each continent should be constructed.

The new mode PANGEA REUSE, giving rise to a completely revised flow, was developed as part of this thesis together with Stephan Held and Max Mundt (also see [\[Mun23\]](#)). Before, every continent was designed separately using the port positions computed by the pangea flow. However, there are chips on which a certain large component occurs multiple times, e.g. when having many processor cores of the same kind. In these cases, it is preferable to only consider one instance of this continent in the later optimization flow. Otherwise, very similar work has to be carried out multiple times. This would lead to a waste of both human and computational resources. On the other hand, several continents which are exactly identical with regards to placement, nets and port configurations can be optimized as one instance. The finished continent will then simply be instantiated multiple times on the final chip.

The key here is to get the port positions to be identical across all equivalent continents. Simply taking the computed result from one of the individual continents is not feasible because of two reasons: To begin with, the ports of a continent must be compatible with those of adjacent continents. Secondly, blindly using the port positions of one of the equivalent continents for the other ones can introduce large source-to-sink detours as well as degrade congestion and net length. PANGEA REUSE solves these issues by taking each instance of the equivalent continents into account.

A further extension of PANGEA REUSE enables even continents that are not 100% equal to be considered equivalent. Tiny differences arise for example when nets need to route through one continent but not through an equivalent one, or when some pin is connected to something outside the continent, but an equivalent pin is not.

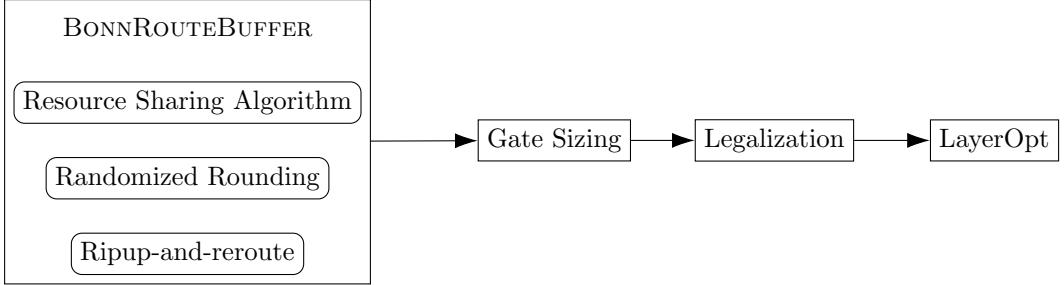

### 2.3.2 BonnRouteBuffer

Timing optimization is one of the largest tasks in chip design. Without taking into consideration how long a signal takes from one pin to another, chips cannot be optimized well. In fact, optimizing congestion and wire length will in many cases actively worsen signal delays. This means that a trade-off is needed. One way to improve delay characteristics of a route is to insert *repeaters* subdividing the wire segments. Repeaters are gates implementing either the inversion function (inverters) or the identity function (buffers). Whenever inverters are used, an even number of them has to be inserted into each source-to-sink path in order to retain the logical function. The reason that repeaters can decrease signal delay is that a gate shields off the capacitance behind it. Without repeaters, signal delay will depend roughly quadratically on the wire length (see Section [2.5](#)). Thus, breaking up a long wire segment and dividing it into several shorter ones can improve timing. In fact, when done optimally, one can achieve a delay that depends only approximately linearly on the wire length [\[Bar+06\]](#).

BONNROUTEBUFFER (see [\[Rot17\]](#), [\[Dab21\]](#) and [\[Dab+23\]](#)) is a powerful tool for inserting repeaters to speed up the signals. In doing so, many constraints and side-objectives are considered: Repeaters can only be placed in such a way that they do not overlap each other or other gates, and a too high placement density will hinder accessing the pins in routing. Furthermore, there are placement blockages forbidding any repeater from being placed in a given area. Additionally, certain thresholds have to be observed giving bounds on capacitance values and signal slews (see Section [2.5](#) for more explanation). In addition to timing itself, BONNROUTEBUFFER takes power

consumption into account as a side-objective. Lastly, net length and wire congestion are considered.

BONNROUTEBUFFER is integrated into the global routing framework described in Section 2.4, meaning that it will route all nets as well as insert repeaters into them. Every time after a net is routed, repeaters are inserted along the route.

When computing routes in the first step, the objectives must already incorporate the fact that repeaters will be inserted as a second step. Therefore, we use a timing model that approximates an optimal repeater placement. This means signal delay is modeled as being linear in the length of a wire. The factors used depend on the exact wire characteristics such as width and layer and are all computed beforehand. However, many nets have more than one sink, hence trees are needed instead of simple paths. A path with many bifurcations will have more signal delay than the very same path without any bifurcations. This is due to the added downstream capacitance given by the paths that are branching off. Hence, it can be beneficial to also keep the number of bifurcations on critical paths in check. Routes going through areas with high placement density or even placement blockages will impede the possibility to insert repeaters. That means such areas have to be considered as well.

Most of these issues need to be addressed by the overall structure of a route, i.e. already in topology generation. When the bifurcation count is considered, it needs to be done in this step as it will remain fixed later on. Whether the route can afford to go over a large placement blockage (where no repeaters can be placed) also needs to be decided in this step. Depending on the main focus of optimization, there are different options for how to compute a good topology. We will discuss these in Section 3.2.

BONNROUTEBUFFER is integrated into a more extensive timing optimization flow called *wire synthesis*. In addition to inserting repeaters, other delay improving techniques are used there: In the process of *gate sizing*, a specific variant (size) for each gate is chosen. Most logic gates exist in multiple different sizes. Apart from in their footprint, these gates differ in certain delay characteristics as well as in their power consumption. So the task of gate sizing is to improve timing while also keeping the power consumption as low as possible. See for example [Dab+18a] and [Dab+18b]. There are also more local improvement strategies that focus on improving the worst path. The *refine placer* moves gates on the worst path in such a way that the wire length and thus also the signal delay on that path are reduced ([Boc+15], [Lüd23]).

Prior to the work on this thesis, BONNROUTEBUFFER was in the state of a prototype. It contained inexact computations and heuristics and was not fine-tuned well. Among other improvements, the slew propagation in both the timing analysis inside BONNROUTEBUFFER as well as the dynamic program computing the actual buffering (the “heart” of BONNROUTEBUFFER) were rewritten to be more exact and thereby allow for a less pessimistic view of slew limits. Additionally, several bugs were fixed in the process of improving its results.

## 2.4 Global routing framework

Global routing is the task of computing the rough position of wire segments connecting given positions on a chip. Instead of considering exact wire locations, each layer of the chip area is cut into rectangles called *tiles*. Connecting adjacent tiles leads to a 3-dimensional grid graph. Since layers only allow for either horizontal or vertical routing in an alternating manner, edges in opposing directions are removed. The resulting graph is called the *global routing graph*. An example global routing graph with few tiles and three layers was already seen in Figure 2.1.

A *pin* is an input or output of a cell. Since cells are already placed inside the chip area when routing is conducted, pins are associated with a position on the chip. While the

actual pin shapes are collections of axis-parallel rectangles, for our purposes it suffices to consider a pin position to be a single point on a given layer. The information how to connect these pins is given by the *netlist*. The netlist consists of many *nets*, which in turn consist of one pin acting as the source and one or more pins representing the sinks of the net. Sources are outputs of cells and sinks are inputs.

Connecting a net with wire makes sure a signal can travel from a cell's output to the corresponding next cells' inputs. We *connect* a net by computing a *global route*. A global route is a Steiner tree inside the global routing graph, where the terminals are the tiles corresponding to the net's pins. Further, we associate a *wire type* with each edge of the route giving details on the wire width, resistance and capacitance. These properties will be needed for the timing analysis, see Section 2.5.

A global route only states through which tiles the final wiring should go, but does not specify the exact routing tracks. This simplification is necessary in order to be able to handle all nets simultaneously. To make sure that it will be possible to compute exact and overlap-free wire positions later on, certain constraints have to be considered. In particular, every global routing edge has a *capacity*, stating how many wires may pass through it.

The goal in global routing is, first and foremost, to find routes for all nets such that the capacity constraints are not violated. Under this constraint, the objective in the simple global routing problem is to minimize net length, i.e. the total summed length of all computed routes. A formal definition of this problem is as follows.

---

### THE SIMPLE GLOBAL ROUTING PROBLEM

**Instance:** A global routing graph  $G = (V, E)$  with edge capacities  $c : E \rightarrow \mathbb{N}$  and a netlist  $\mathcal{N} = (N_i \subset V)_i$ .

**Task:** For every net  $N_i$ , compute a Steiner tree  $R_i$  in  $G$ , such that for each global routing edge  $e \in E$ , we have

$$\sum_i \mathbb{1}_{E(R_i)}(e) \leq c(e).$$

Under all such solutions, minimize

$$\text{net length} := \sum_i \sum_{e \in E(R_i)} \text{length}(e).$$

---

#### 2.4.1 Resource sharing algorithm

As already computing a single minimum-length Steiner tree is NP-hard [Kar72], there is no hope of solving the simple global routing problem exactly in polynomial time. Instead, we will consider a framework that allows us to approximate an optimum solution as well as add further constraints to the problem. For this, we will have a look at the resource sharing algorithm by [MRV11]. The idea is that we have resources  $\mathcal{R}$  which we want to distribute between customers  $\mathcal{C}$ . Each customer has some freedom in regards to its needed resources. Feasible resource allocations for the individual customers are given by closed convex sets  $B_C \subset \mathbb{R}^{\mathcal{R}}$  for each  $C \in \mathcal{C}$ . A feasible resource allocation for all customers  $b : \mathcal{C} \rightarrow \mathbb{R}^{\mathcal{R}}$  assigns to each customer  $C$  a resource allocation  $b(C) \in B_C$  such that  $\sum_{C \in \mathcal{C}} b(C)_r \leq 1$  for each  $r \in \mathcal{R}$ , i.e. such that the total resource usage does not exceed 1 for any resource.

In our case, the global routing edges make up the resources. The customers are given by the nets. Further, for a customer/net  $C$ ,  $B_C$  is the convex hull of incidence vectors of all Steiner trees for  $C$ , where each entry is divided by the capacity of the corresponding edge:

$$B_C := \text{convex-hull} \left( \left\{ \left( \frac{(\chi^F)_r}{c(r)} \right)_{r \in \mathcal{R}} : F \text{ Steiner tree for } C \right\} \right)$$

When defined like this, a total usage of 1 is equivalent to an edge being used to its full capacity, but not beyond. Hence, there is a one-to-one correspondence between feasible resource allocations for all customers and convex combinations of Steiner trees for each net, such that the edge capacities are observed.

To minimize net length, an additional resource representing the net length budget can be added. A good capacity for this resource can be chosen using binary search.

The resource sharing algorithm by [MRV11] maintains prices for the resources and repeatedly calls an oracle (see Section 3.1) to compute minimum-cost resource allocations for the individual customers with regard to these prices. Resource prices are updated multiplicatively in a way such that much demanded resources become more expensive over time. This is done over many phases and in the end, a convex combination containing all computed solutions is returned for every customer. Given that the oracle computes a  $\sigma$ -approximate minimum-cost resource allocation for individual customers, this yields an approximation factor arbitrarily close to  $\sigma$ .

After using the resource sharing algorithm, we end up with a fractional solution. To compute an integral solution, the first step is randomized rounding. After outliers are removed, for each net one of the previously computed Steiner trees is chosen at random. The probabilities are proportional to the factors appearing in the convex combination. This is done separately for each net. Using a result from [RT87], this results in a solution that does not violate many resource capacities.

The remaining violations are fixed by a ripup-and-reroute procedure recomputing solutions for individual nets.

### 2.4.2 Arrival time customers

The model so far can compute routes for all nets while minimizing net length and keeping the wiring congestion feasible. However, there is no mechanism controlling the time a signal needs from its start to its endpoint. But this is a crucial characteristic of a route and especially needed in BONNROUTEBUFFER.

The approach used throughout this thesis was introduced by [Hel+18]. In addition to the routing resources for the global routing edges and the net length budget, there are *timing resources*: We add one timing resource for every sink in each net. This resource represents the delay budget that a signal has to traverse the net to the given sink. With only these resources, the timing of different nets is still separate. To overcome this problem, *arrival time customers* are used as additional customers. One arrival time customer is added for each gate. The set of feasible solutions for an arrival time customer is a time interval inside which the signal can arrive at the associated gate. The earlier the chosen solution lies inside this interval, the more usage it takes from the timing resources going into the gate. Vice versa, a late solution takes more usage from the timing resources leaving the gate. As shown in [Hel+18], the existence of feasible arrival times at the gates ensures that overall timing constraints are met.

### 2.4.3 Incorporating further constraints

In BONNROUTEBUFFER, placement and power constraints are considered next to routing congestion and timing. Both can be incorporated into the global routing framework

natively.

For placement, it is important that the footprints of all gates fit into the area where they were placed. To model area locally as opposed to only making sure all gates can be placed *somewhere* on the chip, the chip area is cut into placement bins. Often times, these are the same as the global routing tiles. Each placement bin is associated with a separate placement resource. Its capacity depends on the size of the bin and overlapping placement blockages. Whenever a repeater is placed during BONNROUTEBUFFER, the solution has to pay a cost according to the size of the repeater relative to the surrounding placement bin.

Incorporating the consideration of power requires some assumptions to be made. When a power budget is given, it is possible to add a single resource representing power with that capacity. Every route then consumes of this resource exactly the route's power consumption divided by the power budget. In the end, feasibility for the power resource translates directly to the power budget being observed. However, no set budget for power consumption is given. Rather, the solution should have a reasonable power consumption while satisfying the other constraints. In practice, this is achieved by estimating a power budget and adjusting it in every phase of the resource sharing algorithm.

## 2.5 Timing

This section will introduce notions regarding signals and their delay properties. For this, we will assume routes to be directed away from the source.

A *signal* is a voltage change from 0 to  $V_{dd}$  (the chip's operating voltage) or vice versa. A voltage change from 0 to  $V_{dd}$  is called a *rise signal*, a change from  $V_{dd}$  to 0 is called a *fall signal*. When a signal arrives at the source of a net, it will be transmitted to the sink of said net after a short delay. Similarly, a signal can go from an input to an output of a gate. The *arrival time* of a signal at some position is the point in time when the voltage crosses the 50%  $V_{dd}$  threshold at that position. The arrival time at a pin  $p$  is denoted as  $at(p)$ . The *delay* from pin  $p_1$  to pin  $p_2$  is the difference in arrival times at these points:  $delay(p_1, p_2) = at(p_2) - at(p_1)$ . We speak of *wire delay* if the pins are on the same wire path, and of *gate delay* for the time a signal takes to go from a gate's input to the output.

For primary input pins, the arrival times are given in the input. Given delay functions (e.g. by a timing model on fixed routes), we can then compute the arrival times of all pins.

*Required arrival times* state the latest point in time at which a signal should arrive. The required arrival time of a pin  $p$  is denoted by  $rat(p)$ . Required arrival times for primary outputs are given in the input. Required arrival times on the other pins can then be computed given the delay functions of a timing model.

For any given pin  $p$ , we define the *slack* to measure how much later the signal is allowed to arrive at  $p$  compared to the current arrival time:  $slack(p) := rat(p) - at(p)$ . If the slack is non-negative at all pins, every signal arrives in time.

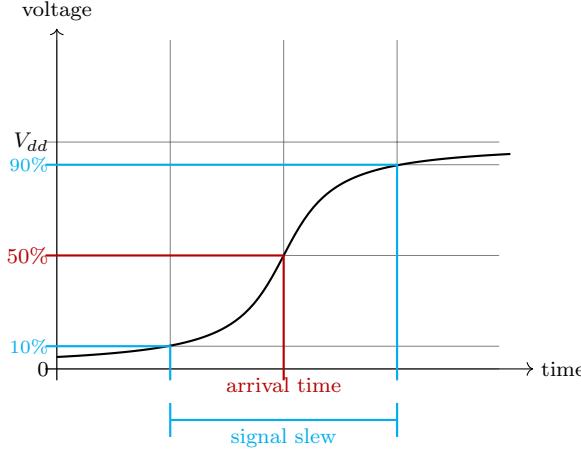

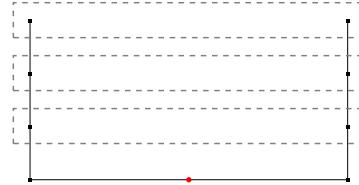

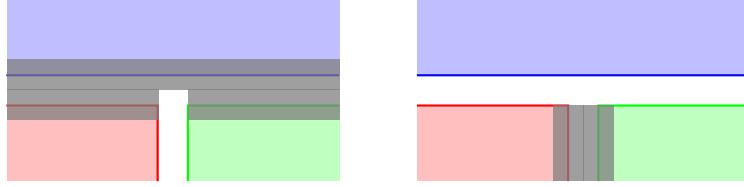

A further important property of a signal is its *slew*, which is the time the voltage is inside the  $[10\% V_{dd}, 90\% V_{dd}]$  interval. Both arrival time and slew are marked on an example signal slope in Figure 2.2. In general, a steeper, i.e. smaller, slew leads to faster signals. Once the slew of a signal crosses a given threshold, the *slew limit*, there is a *slew violation*. The value of the slew violation is given by  $slew - slew\_limit$ .

Each wire segment further has *capacitance* and *resistance* values. Gate inputs and primary outputs also have a *capacitance* value. The *downstream capacitance* of any point in a route is the sum over all the capacitances of wire segments and pins that can be reached from the point through wiring (see Section 2.5.1). As for slew values, the

**Figure 2.2:** An example slope of a rise signal. The arrival time is marked at the 50%  $V_{dd}$  threshold. The signal slew is marked as the interval between the 10% and 90% voltage thresholds.

downstream capacitance also must not exceed a certain threshold called the *load limit*. Otherwise, a *load violation* occurs, where again the value of the violation is given by *downstream\_capacitance – load\_limit*.

### 2.5.1 Elmore delay model

A simple yet quite precise model to describe signal delays is the *Elmore delay model* introduced in [Elm48]. This delay model, also called the *RC-delay model*, models a wiring tree with gates by resistors and capacitors.

We will use the following notation to formally define the Elmore delay. Fix a wiring tree  $Y$  rooted at its source  $r$ . For a vertex  $v \in V(Y)$ , let  $Y_v$  denote the sub-tree of  $Y$  rooted at  $v$ . Further, let  $\text{downcap}(v)$  be the downstream capacitance of  $v$ , which we define recursively by

$$\text{downcap}(v) = \begin{cases} \text{cap}(v) & \text{if } v \text{ is a sink,} \\ \sum_{w \in \Gamma^+(v)} \text{cap}(v, w) + \text{downcap}(w) & \text{else,} \end{cases}$$

where  $\text{cap}(v, w)$  denotes the wire capacitance of the  $(v, w)$ -segment.

For an edge  $(v, w)$  in  $Y$ , we can now define the RC-value of the edge by

$$\text{RC}_Y(v, w) := \text{res}(v, w) \cdot \left( \frac{\text{cap}(v, w)}{2} + \text{downcap}(w) \right).$$

We naturally extend this by

$$\text{RC}_Y(v, w) := \sum_{(p, q) \in E(P_{[v, w]})} \text{RC}_Y(p, q),$$

where  $P_{[v, w]}$  denotes the unique path in  $Y$  from a node  $v$  to some  $w$  in  $Y_v$ . The wire delay between nodes  $v$  and  $w$  according to the Elmore model becomes

$$\text{wire-delay}_Y(v, w) := \ln 2 \cdot \text{RC}_Y(v, w).$$

For the slew degradation, we will use Bakoglu's metric [Bak90]

$$\text{slew-deg}_Y(v, w) := \ln 9 \cdot \text{RC}_Y(v, w),$$

and define the out-slew at  $w$ , given an in-slew at  $v$ , as in [Kas+04]:

$$\text{out-slew}_Y(v, w, \text{in-slew}) := \sqrt{\text{in-slew}^2 + (\text{slew-deg}_Y(v, w))^2}.$$

For a gate  $g$ , we will assume a resistance  $\text{res}(g)$  to be given. Then the delay through  $g$  is defined by

$$\text{gate-delay}(g) := \text{res}(g) \cdot \text{downcap}(g).$$

### 2.5.2 Linear delay model

An even simpler delay model is the linear delay model. Here, we assume the signal delay to increase linearly in the wire length, while gate delays are being neglected. The signal speed can vary depending on layer and wire type.

Using a linear delay model is justified for estimating delay in unbuffered scenarios, as proper buffering will lead to near-linear delays. As done in [Bar+06], factors describing the delay per length can be estimated by buffering very long wire segments and calculating the average delay per length.

For the purpose of this thesis, we will say that *linear timing data* is a function

$$\text{lin-delay} : \text{Layers} \times \text{WireTypes} \rightarrow \mathbb{R}^+$$

mapping a layer and wire type to  $\mathbb{R}^+$ , which we will interpret as the *delay per length* of the wire type on the given layer.

# Chapter 3

## Algorithms for timing-constrained global routing

### 3.1 Global routing oracle

As outlined in Section 2.4.1, the resource sharing algorithm makes use of an oracle for computing minimum-cost routes for the considered nets. Put formally, when considering routing and timing resources, the oracle needs to solve the following problem.

---

#### ROUTING PROBLEM INSIDE RESOURCE SHARING

**Instance:** The global routing graph  $G = (V, E)$ , a net  $N$  with specified source  $r$  and sinks  $T$ , congestion prices  $c : E \rightarrow \mathbb{R}^+$  and delay weights  $w : T \rightarrow \mathbb{R}^+$ .

**Task:** Compute a Steiner tree  $Y$  for the net  $N$  minimizing

$$\sum_{e \in E(Y)} c(e) + \sum_{t \in T} w(t) \cdot \text{delay}_Y(r, t),$$

where  $\text{delay}_Y(r, t)$  denotes the delay through  $Y$  from the net source  $r$  to the sink  $t$ .

---

The exact definition of  $\text{delay}_Y(r, -)$  depends on the timing model used. The simplest version to think of would be to set  $\text{delay}_Y(r, -) \equiv \text{dist}_Y(r, -)$ . Details on timing models are given in Section 2.5.

As already seen in Section 2.2, the oracle considered in this thesis to compute an approximately minimum-cost route for each net consists of two main steps. First, a Steiner tree for the given net is computed in  $(\mathbb{R}^2, \ell_1)$ . This Steiner tree is called the *topology*. Afterwards, the tree is embedded into the global routing graph by successive Dijkstra searches. This is based on [Hel+18].

#### 3.1.1 Topology generation

During topology generation, a Steiner tree is computed in  $(\mathbb{R}^2, \ell_1)$  for the given net. Different possibilities for both optimization objectives and respective algorithms how to compute this Steiner tree are presented in Section 3.2.

---

**Algorithm 1:** Topology embedding algorithm [Hel+18]

---

**Input:** Global routing graph  $G = (V, E)$ , source  $r \in V$ , sinks  $T \subset V$ , binary arborescence  $Y$  with a mapping  $p : V(Y) \rightarrow V$  such that  $p(\text{root}(Y)) = r$  and the leaves of  $Y$  are bijectively mapped to  $T$ .

**Output:** An arborescence  $Y'$  in  $G$  with root  $r$  and leaves  $T$ .

```

1  $\text{labels}(v) := \{(p(v), 0)\}$  if  $v$  is a leaf and  $\text{labels}(v) := \emptyset$  else for all  $v \in V(Y)$

2 foreach  $v \in V(Y)$  in reverse topological order do

3    $\text{targets} :=$  the set of all vertices with the same x and y coordinates as  $p(v)$

4    $\text{heap} :=$  empty-heap

5   foreach  $c \in \Gamma^+(v)$  do

6      $\text{insert all elements of } \text{labels}(c) \text{ into the } \text{heap}$

7   while not all targets are permanently labeled do

8      $\text{propagate the minimum-cost label in } \text{heap}$

9    $\text{labels}(v) := \{ (p(x), \text{cost}(l_1) + \text{cost}(l_2)) \mid l_1, l_2 \text{ permanent labels at } x \in V$

$\text{from paths starting at both children of } v \}$

10 back-track the minimum-cost label in  $\text{labels}(r)$  to create  $Y'$

11 return  $Y'$

```

---

For the subsequent embedding, it is necessary that the topology fulfills these structural constraints:

- Every vertex has out-degree at most 2 and

- the leaves are exactly the sinks.

Any tree can be transformed into one fulfilling these constraints in linear time without changing the total net length. This is done by adding vertices on top of existing vertices and edges of length 0.

### 3.1.2 Embedding

After the computation of a 2-dimensional Steiner tree, each edge needs to be embedded into the global routing graph. The embedding needs to decide the exact global routing edges to use and which wire type to use on which edge. Additionally, the final Steiner point locations are decided during the embedding.

The rough outline of the algorithm can be seen in Algorithm 1. In Line 1, we initialize labels of cost 0 for all sinks. Then, we traverse the nodes of  $Y$  in reverse topological order. For each  $v \in V(Y)$ , we do the following. We initialize the targets to be all global routing nodes at the same x and y coordinates as  $p(v)$  (Line 3). In particular, the targets can lie on different layers. We also initialize an empty heap and insert the elements of  $\text{labels}(c)$  for each child  $c$  of  $v$  into the heap (Lines 4-6). We then propagate the minimum-cost label in the heap along all adjacent edges as long as not all targets are permanently labeled (Lines 7 and 8). Finally, we merge permanent labels coming from different children of  $v$  to create  $\text{labels}(v)$  by setting

$$\text{labels}(v) := \{ (p(x), \text{cost}(l_1) + \text{cost}(l_2)) \mid l_1, l_2 \text{ permanent labels at } x \in V \\ \text{from paths starting at both children of } v \}.$$

When we have reached the source, we retrieve the final result via back-tracking from the minimum-cost label in  $\text{labels}(r)$  (Lines 10 and 11).

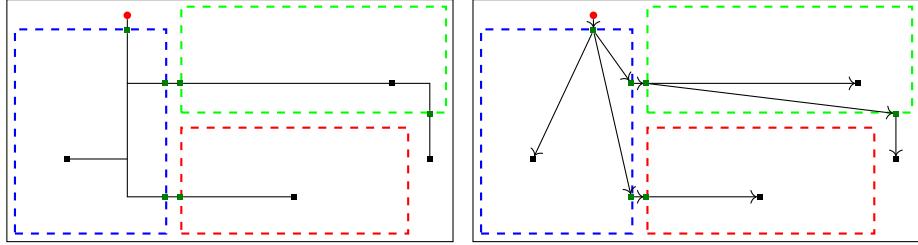

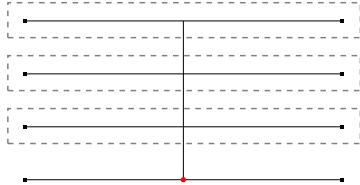

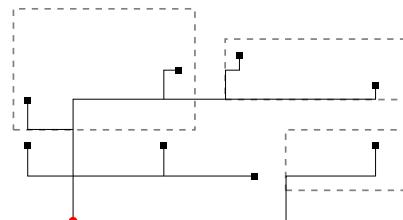

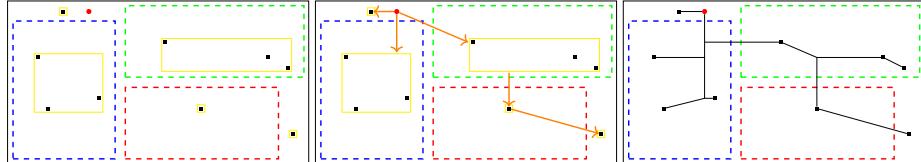

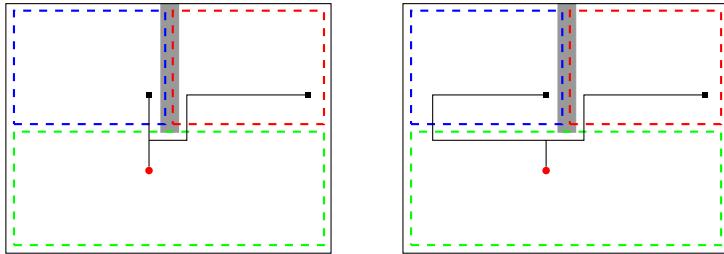

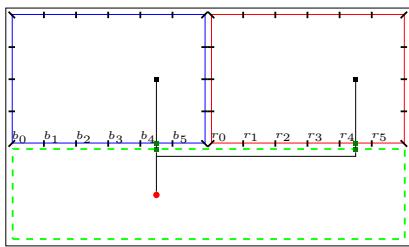

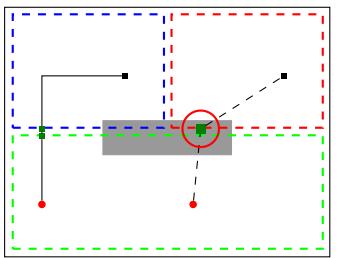

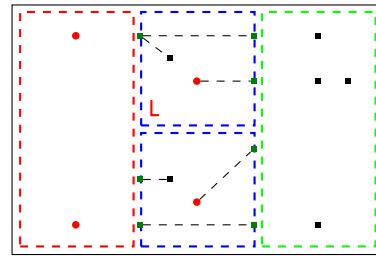

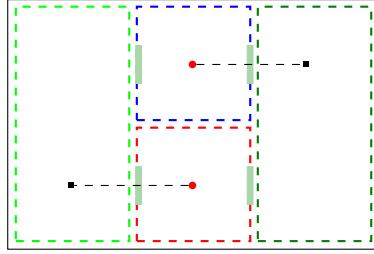

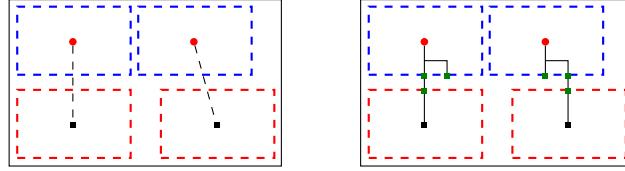

**Figure 3.1:** Example net with a blockage-unaware topology (left) and a blockage-aware topology (right). The gray shape represents a blockage. When embedding the left tree, the edge going to  $s_2$  will have to be routed around that blockage. The blockage-aware topology prevents this issue.

The crucial parts are traversing the topology in reverse topological order and starting from all found permanent labels in the next Dijkstra searches to not fix final Steiner point positions too early. During labeling, the global routing graph is considered to have parallel edges between adjacent vertices wherever a choice between multiple wire types arises. The cost function used during the Dijkstra searches depends on the current use case. Resource prices for net length and routing congestion are always considered. In BONNROUTEBUFFER, additionally the prices for timing, power and placement are taken into account.

## 3.2 Topology algorithms

Many different options arise for computing a “good” topology in global routing. In this section, we will first consider Steiner tree algorithms dealing with several kinds of blockages. After that, we will present Steiner tree algorithms that can consider additional input from arrival time customers or delay prices.

### 3.2.1 Reachaware topologies

When only routing congestion and net length play a role, the routing problem itself reduces to a Steiner-minimum-tree (SMT) problem. Hence also the topology can be computed using an SMT approximation algorithm.

However, there are further circumstances that are reasonable to consider: When there is a blockage covering all routing layers in a given area, it is beneficial for the topology generation to already take this into account. Otherwise, the embedding might have to route large detours that could have been easily avoided by changing the structure of the Steiner tree. An example for such a situation is shown in Figure 3.1.

Moreover, there are situations in which not all layers, but all layers of a given direction are blocked for routing. This translates to orientation-restricted blockages in topology generation, i.e. blockages that forbid either horizontal or vertical segments through them.

Lastly, there can be placement blockages. Then, routing is allowed, but no repeaters may be inserted there. Connected components of wiring on a placement blockage need to be driven by a single repeater. This leads to an upper bound of capacitance of connected wiring inside the blockage. The upper bound is given by the capacitance limits of the strongest repeater. As capacitance is linear in the wire length, this is modeled by restricting the length of a connected component inside such a blockage.

These considerations give rise to the REACHAWARE STEINER TREE PROBLEM:

---

## REACHAWARE STEINER TREE PROBLEM

**Instance:** Sets  $\mathcal{R}_l, \mathcal{R}_h, \mathcal{R}_v \subset \mathbb{R}^2$  that are the union of finitely many axis-parallel rectangles, a finite set of terminals  $T \subset \mathbb{R}^2$  and  $L \in \mathbb{R}^+$ .

**Task:** Compute a shortest *reachaware* Steiner tree for  $T$ , i.e. a rectilinear tree  $Y$  satisfying that

1. every edge in  $E(Y) \cap \mathcal{R}_h^o$  is horizontal,

2. every edge in  $E(Y) \cap \mathcal{R}_v^o$  is vertical and

3. every connected component of  $E(Y) \cap (\mathcal{R}_l \cup \mathcal{R}_h \cup \mathcal{R}_v)^o$  has total length  $\leq L$ .

---

[Bih15], extending upon [HS14], gives a polynomial-time 2-approximation algorithm for the case where no terminals lie inside  $(\mathcal{R}_l \cup \mathcal{R}_h \cup \mathcal{R}_v)^o$ . This algorithm works by constructing a *visibility graph* and computing a terminal spanning tree in there. In addition to the terminals, the visibility graph contains certain vertices on the border of the given restriction sets.

Under co-supervision of the author of this thesis, an adaptation of this algorithm was developed and implemented computing reachaware shortest-path trees in [Rei23]. In this version of the problem, one of the terminals  $T$  is the designated root  $r$  and the resulting tree must contain (reachaware) shortest paths from  $r$  to all other terminals. This is important for practical application as short paths are necessary for fast signals.

Similarly to [Rao+92], *sink pairs* are chosen iteratively and a common *parent* is inserted. A sink pair is a pair of vertices in the current branching that do not have an incoming edge. A parent of a sink pair is a node lying on shortest paths from the root to both sinks, and among all these, one that is furthest from the root. The sink pair of each iteration is chosen such that the common parent vertex has maximum distance to the root.

This algorithm yields a 2-approximation on instances where the following holds:

- a)  $T \subset \mathbb{R}^2 \setminus (\mathcal{R}_l \cup \mathcal{R}_h \cup \mathcal{R}_v)^o$ ,

- b) all terminals and blockages lie in the first quadrant,

- c) blockages are disjoint rectangles,

- d)  $\mathcal{R}_l = \emptyset$  and  $\mathcal{R}_h = \mathcal{R}_v$ .

Here, the last constraint makes sure that area is either not blocked at all or completely blocked.

The algorithm by [Rei23] can be improved further in the following way. In practice, the topology is not required to contain strictly shortest paths. Instead, a small detour (relative or absolute) is often allowed. This is sensible in our use-case, as the subsequent embedding will not adhere exactly to the Steiner point positions in any case. Simply changing the definition of a parent to also allow small detours will not lead to good solutions, though. Instead, the choice of the sink pair and the parent location have to be separated. As previously, the sink pair for which a parent is added is chosen such that the parent location (with the previous definition) is furthest from the root. But instead of placing the parent node at that location, it can be moved to minimize net length instead of maximizing its distance to the root, under the restriction that the detour does not become too large. To be exact, the parent location  $p$  is chosen so that it minimizes

$$d(r, p) + d(p, s_1) + d(p, s_2)$$

under all feasible locations for a fixed sink pair  $s_1, s_2$ .

Note that this choice coincides with maximizing the distance between parent and root if no detour is allowed:

**Proposition 3.1.** *Given a graph  $G = (V, E)$  with edge lengths  $d : E \rightarrow \mathbb{R}^+$ , a root  $r \in V$  and two sinks  $s_1, s_2 \in V$ , define  $P \subseteq V$  to be all nodes lying on a shortest  $r$ - $s_1$ -path and a shortest  $r$ - $s_2$ -path. Then*

$$\operatorname{argmin}_{p \in P} (d(r, p) + d(p, s_1) + d(p, s_2)) = \operatorname{argmax}_{p \in P} d(r, p).$$

*Proof.* By the definition of  $P$ , we know  $d(p, s_i) = d(r, s_i) - d(r, p)$  for  $i = 1, 2$  and  $p \in P$ . Hence

$$\begin{aligned} & \operatorname{argmin}_{p \in P} (d(r, p) + d(p, s_1) + d(p, s_2)) \\ &= \operatorname{argmin}_{p \in P} (d(r, p) + (d(r, s_1) - d(r, p)) + (d(r, s_2) - d(r, p))) \\ &= \operatorname{argmin}_{p \in P} (d(r, s_1) + d(r, s_2) - d(r, p)) \\ &= \operatorname{argmax}_{p \in P} d(r, p) \end{aligned}$$

as claimed. □

Further, the running time of the implementation by [Rei23] can be improved significantly. Instead of computing the parent location of all sink pairs in advance (and maintaining this set when parent nodes are added as terminals), it suffices to compute which parent to consider next. This can be done efficiently by traversing the nodes in descending order of distance to the root, so that we can stop as soon as the considered nodes are closer to the root than the currently best found parent.

### 3.2.2 Timing-aware topologies

When timing is considered explicitly, two main options are interesting in the context of this thesis. One possibility is to use a bi-criteria algorithm such as described in [KRY95] or [HR13]. Such an algorithm approximately minimizes total tree length under the restriction that source-to-sink distances are bounded.

Instead of considering bounds, delay weights can be given on the sinks. Then, it is the objective to minimize a weighted sum of net length and source-to-sink distances. The resulting problem is called the cost-distance Steiner tree problem, which was first introduced in [MMP08]. This version more closely resembles the task given in the global routing oracle, as delay weights are given by the timing prices.

Other important algorithms for industrial application can be found in [Bar+06], [CTY17], [Alp+95] and [Alp+18].

#### Bi-criteria

A simple version of the topology problem with delay bounds can be defined as follows.

---

## SHALLOW-LIGHT STEINER TREE PROBLEM

**Instance:** A metric space  $(M, d)$  (usually  $(\mathbb{R}^2, \ell_1)$ ), a root  $r \in M$  and finitely many terminals  $T \subset M$  together with delay bounds  $rat : T \rightarrow \mathbb{R}^+$ .

**Task:** Compute a Steiner tree  $Y$  rooted at  $r$  with leaves  $T$  satisfying

$$\sum_{e \in P_{[r,t]}} d(e) \leq rat(t) \quad \forall t \in T,$$

where  $P_{[r,t]}$  is the (unique)  $r$ - $t$ -path in  $Y$ , such that  $Y$  minimizes  $d(Y)$ .

---

Here, we implicitly assume an embedding  $p : V(Y) \rightarrow M$  that maps  $r$  and the terminals to themselves. We write  $d(e) = d(p(v), p(w))$  for an edge  $e = \{v, w\}$ .

[KRY95] consider the case that  $M = \{r\} \cup T$ . For a given  $\varepsilon > 0$ , they compute a solution tree of length at most  $(1 + \frac{2}{\varepsilon}) \cdot MST$ , such that every  $r$ - $t$ -path has length at most  $(1 + \varepsilon) \cdot \text{dist}_{(M,d)}(r, t)$ . Here,  $MST$  denotes the length of a minimum spanning tree.

An extension of this problem is considered in [HR13], where additionally to the root-to-terminal distance, bifurcation delays are taken into account. When requiring that the tree is binary and assuming a bifurcation delay of  $b > 0$ , the feasibility constraint becomes

$$delay_Y(t) := \sum_{e \in P_{[r,t]}} d(e) + b \cdot \text{bif}_Y(t) \leq rat(t) \quad \forall t \in T,$$

where  $\text{bif}_Y(t)$  denotes the number of bifurcations on the  $r$ - $t$ -path in  $Y$ . [HR13] show how to compute a Steiner tree  $Y$  of length at most

$$\left(1 + \frac{2}{\varepsilon}\right) \text{length}(Y_0) + \frac{4b \cdot |T|}{\varepsilon},$$

where  $Y_0$  is an initial (short) Steiner tree, such that

$$\min_{t \in T} rat(t) - delay_Y(t) \leq -2b - \varepsilon \cdot \max_{t \in T} rat(t).$$

For well chosen distance/delay bounds, very good topologies can be found in practice with this approach. A feasible choice for the distance bounds is to use the already computed interval bounds of the arrival time customers at the net's sinks. These interval bounds can be multiplied by a factor depending on the timing criticality of the net. The bifurcation delay can be used to simulate the fact that side-branches add to the downstream capacitance and hence increase the actual delay after buffering.

While this approach does perform well in practice, it cannot distinguish between the timing criticalities of individual sinks of the same net due to the choice of delay bounds. Either the entire net is considered critical and all paths are kept short, or all source-to-sink paths are allowed to contain more detour. Additionally, the resource prices for sink delay are not considered at all in this formulation. One way to include information about individual timing criticalities would be to replace the interval bounds of the arrival time customers by the actual chosen arrival times, i.e. set  $rat(t) = at(t) - at(r)$ , where  $at(t)$  and  $at(r)$  are the current (fractional) solutions of the respective arrival time customers. However, this would be highly heuristic and might lead to negative delay budgets. To eliminate these problems, the delay prices given by the resource sharing algorithm have to be employed directly.

### Cost-distance

When considering delay weights and equating delay and distance, the arising problem is exactly the uniform cost-distance Steiner tree problem (see [MMP08] and [KH20]):

---

#### UNIFORM COST-DISTANCE STEINER TREE PROBLEM

**Instance:** A graph  $G = (V, E)$ , a source  $r \in V$  and sinks  $T \subseteq V$ , edge costs  $c : E \rightarrow \mathbb{R}^+$  and delay weights  $w : T \rightarrow \mathbb{R}^+$ .

**Task:** Compute a Steiner tree  $Y$  for  $\{r\} \cup T$  minimizing

$$\sum_{e \in E(Y)} c(e) + \sum_{t \in T} w(t) \cdot \text{dist}_{(Y, c)}(r, t),$$

where  $\text{dist}_{(Y, c)}(r, t)$  denotes the length of the unique  $r$ - $t$ -path in  $Y$  with respect to  $c$ .

---

This problem can be solved up to a factor of 2.05 within  $\mathcal{O}(\Lambda + |T|)$  time, where  $\Lambda$  denotes the time for computing an approximate shortest Steiner tree, see Section 3.3.

In practice, edge *cost* as in the first summand and edge *delay* as in the second summand of the objective function need not coincide. An alternative router solving the non-uniform cost-distance Steiner tree problem, where these two can be unrelated, is presented in Section 3.4. When they only differ by a constant factor, the ratio can be incorporated into the delay weights to remain with the original uniform problem.

Balancing edge costs and delays this way is difficult to do well in practice. When topologies are computed using the uniform cost-distance algorithm from Section 3.3 in BONNROUTEBUFFER, the edge costs are taken to be the average edge cost of a previously embedded solution, while edge delays are given by the linear timing data.

### 3.3 Tighter approximation for the uniform cost-distance Steiner tree problem

This section is joint work with Stephan Held and Yannik Spitzley. The results are already published in [FHS23]. They improve upon preliminary results in [HS22]. We jointly developed the cutting criterion (Algorithm 3). The author of this thesis contributed in simplifying the analysis compared to [HS22] and the tightness proof. The latter was not yet a part of [HS22].

#### 3.3.1 Main theorems

**Theorem 3.2.** *The UNIFORM COST-DISTANCE STEINER TREE PROBLEM can be approximated in polynomial time with an approximation factor of*

$$\beta + \frac{\beta}{\sqrt{\beta^2 + 1 + \beta - 1}},$$

where  $\beta \geq 1$  is the approximation guarantee for the minimum-length Steiner tree problem.

With the best known approximation factor for the minimum Steiner tree problem  $\beta = \ln(4) + \epsilon$  [Byr+13; TZ22], this results in an approximation factor <2.05 and for  $\beta = 1$  this gives the factor  $1 + \frac{1}{\sqrt{2}} < 1.71$ , clearly improving upon the previously best

factors 2.39 and 2.0 in [KH20]. The polynomial-time approximation scheme by [Aro98] allows choosing  $\beta$  arbitrarily close to one in the Euclidean and the Manhattan planes. However, general metric spaces do not allow  $\beta \leq \frac{96}{95}$  unless  $P = NP$  [CC08].

Assuming an ideal Steiner tree approximation factor of  $\beta = 1$ , our new approximation factor is tight with respect to the lower bound  $C_{SMT}(T \cup \{r\}) + D(T, r, w)$ , where  $C_{SMT}(T \cup \{r\})$  is the connection cost of a minimum-length Steiner tree for  $T \cup \{r\}$ , i.e. a Steiner tree  $Y$  for  $T \cup \{r\}$  minimizing  $\sum_{e \in E(Y)} c(e)$ , and  $D(T, r, w) := \sum_{t \in T} w(t)c(r, t)$  is the sum of weighted root-sink distances.

**Theorem 3.3.**

$$\sup_{T, r, w} \frac{\text{OPT}(T, r, w)}{C_{SMT}(T \cup \{r\}) + D(T, r, w)} = 1 + \frac{1}{\sqrt{2}},$$

where  $\text{OPT}(T, r, w)$  denotes the optimum solution value for an instance  $(T, r, w)$  of the UNIFORM COST-DISTANCE STEINER TREE PROBLEM. Theorem 3.3 is proven in [FHS23]. The part of proof that does not need Theorem 3.2 was already contained in [Foc20] and is therefore not a part of this thesis.

### 3.3.2 The $(1 + \beta)$ -approximation algorithm

For shorter formulas, we will use the following notation in the remainder of Section 3.3. Let  $A$  be an arborescence. By  $A_v$  we denote the sub-arborescence rooted at  $v$ . Furthermore,  $T_A := V(A) \cap T$  is the set of terminals in  $A$ ,  $W_A := w(T_A)$  is the sum of delay weights in  $A$ ,  $C_A := c(E(A))$  is the *connection cost* of  $A$  and  $D_A := D_{T_A} := \sum_{t \in T_A} w(t)c(r, t)$  the *minimum possible delay cost* for connecting the sinks in  $T_A$  (independent of the structure of  $A$ ).

Recall that  $\beta \geq 1$  is the approximation guarantee for the minimum-length Steiner tree problem. The algorithm in [KH20] is described in Algorithm 2. After orienting its edges, we can consider any solution  $A$  as an  $r$ -arborescence. We use arborescences instead of trees to simplify the algorithmic notation.

#### Essential steps for a $1 + \beta$ approximation

We quickly recap the essential steps in the analysis of [KH20], which we will use in our analysis. The cost to connect an arborescence  $A' \in \mathcal{A}$  to the root  $r$  can be estimated as follows:

**Lemma 3.4** ([KH20], Lemma 1). *Let  $A' \in \mathcal{A}$  with corresponding terminal set  $T'$ . By the choice of the port  $t \in T'$ , the  $r$ -arborescence  $(A' + \{r, t\})$  has a total cost at most*

$$C_{A'} + \sum_{e=(x,y) \in E(A')} \frac{2W_{A'_y}(W_{A'} - W_{A'_y})}{W_{A'}} c(e) + \left(1 + \frac{1}{W_{A'}}\right) D_{T'} \quad (3.1)$$

$$\leq \left(1 + \frac{W_{A'}}{2}\right) C_{A'} + \left(1 + \frac{1}{W_{A'}}\right) D_{T'} \quad (3.2)$$

$$\leq (1 + \mu) C_{A'} + \left(1 + \frac{1}{\mu}\right) D_{T'}. \quad (3.3)$$

For a proof sketch, see the appendix in [FHS23]. We use the bounds (3.1) and (3.2) that were not stated explicitly in [KH20], Lemma 1. While the bounds (3.1) and (3.2) hold for any (sub-)arborescence  $A'$ , (3.3) depends on the specific way how  $A' \in \mathcal{A}$  was cut off during Step 2 of Algorithm 2.

A similar cost bound can be shown easily for the arborescence  $A_r$  containing the root  $r$  after Step 2. Summing up the resulting cost bounds and choosing  $\mu = \frac{1}{\beta}$ , [KH20] obtain the approximation factor  $(1 + \beta)$ .

---

**Algorithm 2:**  $(1 + \beta)$ -approximation algorithm by [KH20] using a parameter  $\mu > 0$ .

---

**Step 1 (initial arborescence):**

First, compute a  $\beta$ -approximate minimum cost Steiner  $r$ -arborescence  $A_0$  for  $T \cup \{r\}$  with outdegree 0 at all sinks in  $T$  and outdegree 2 at all Steiner vertices in  $V(A_0) \setminus (T \cup \{r\})$ .

**Step 2 (split into branching):**

Traverse  $A_0$  bottom-up. For each traversed edge  $(x, y) \in E(A_0)$ , if  $W_{(A_0)_y} > \mu$ , remove the edge  $(x, y)$  creating a new arborescence  $(A_0)_y$  in the branching.

Let  $\mathcal{A}$  denote the set of all arborescences that were cut off from  $A_0$  this way.

**Step 3 (reconnect arborescences):**

Reconnect each sub-arborescence  $A'$  that was cut off in Step 2 as follows: Select a vertex  $t \in T' := T_{A'}$  that minimizes the cost for serving the sinks in  $T'$  through the  $r$ -arborescence  $A' + (r, t)$ , i.e. select a vertex  $t \in T'$  as a *port* for  $T'$  that minimizes

$$c(r, t) + C_{A'} + \sum_{t' \in T'} w(t') \cdot (c(r, t) + c(E(A'_{[t, t']}))).$$

Let  $t_1, \dots, t_{|\mathcal{A}|} \in T$  be the set of selected port vertices. Return the union of the final branching and the port connections  $A_0 + \{(r, t_i) : i \in \{1, \dots, |\mathcal{A}|\}\}$ .

---

### 3.3.3 Improving the approximation ratio

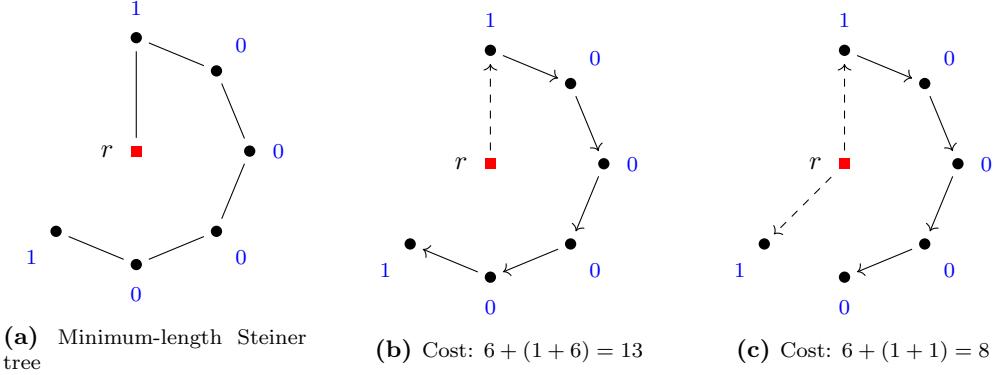

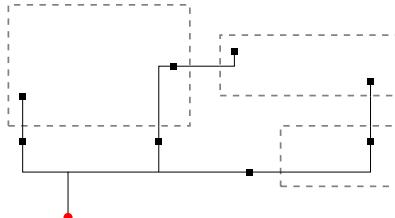

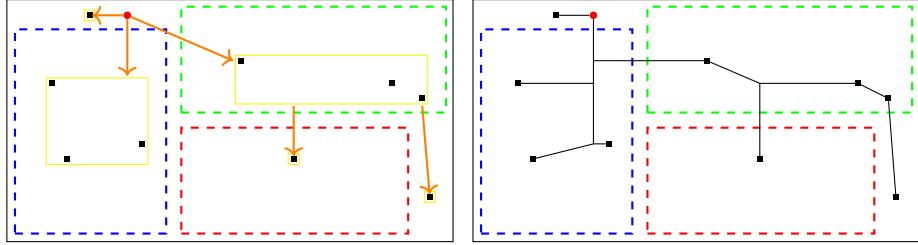

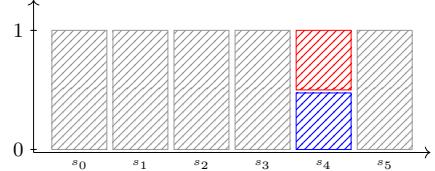

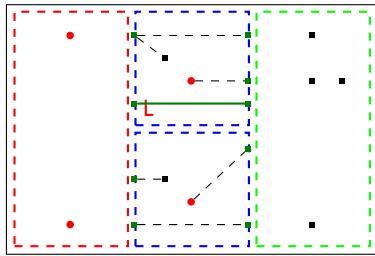

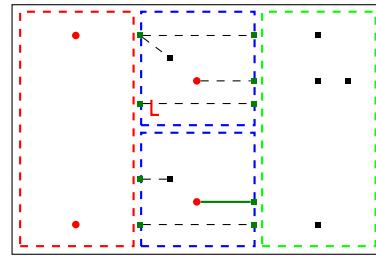

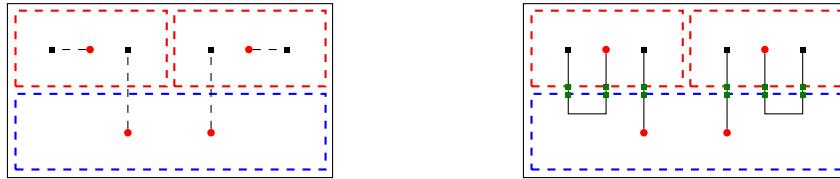

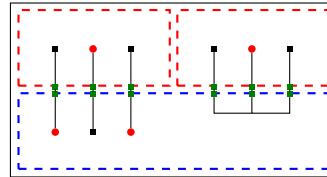

Algorithm 2 suffers from the following weakness indicated in Figure 3.2. Assume that after splitting we are given a sub-arborescence  $A' \in \mathcal{A}$  with a high delay weight  $W_{A'}$ , a high connection cost  $C_{A'}$ , but a low minimum possible delay cost  $D_{A'}$ , e.g. as shown in Figure 3.2b. Then Algorithm 2 would retain the high delay cost. Instead, it would be better to split the arborescence further to achieve a lower delay cost as in Figure 3.2c.

In this section, we propose a refined splitting criterion that provides a better approximation ratio. Instead of using a fixed threshold  $\mu$ , we allow to split off sub-arborescences earlier if their expected reconnection cost (3.1) is sufficiently cheap. The precise criterion is specified in (3.4) (inside Algorithm 3). Observe that (3.4) provides cheaper solutions than (3.3), as one occurrence of  $\mu$  is replaced by  $\frac{\mu}{2}$ .

Then we show in Lemma 3.8 that every sub-arborescence of the remaining root component has delay weight at most  $\mu$ . This allows us to prove a similar improved cost bound for the root component in Lemma 3.9.

Finally, we simply combine all sub-arborescences and choose  $\mu$  to prove Theorem 3.2.

#### Improving the splitting routine

Algorithm 3 shows our improved splitting step, which cuts off a sub-arborescence if we can reconnect it cheaply, i.e. if (3.4) holds. With Lemma 3.4 we immediately get the following result for the cut-off sub-arborescences:

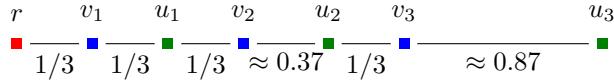

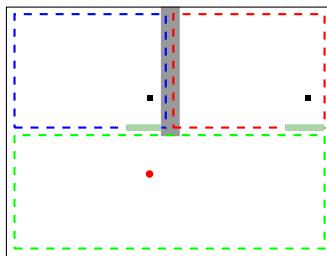

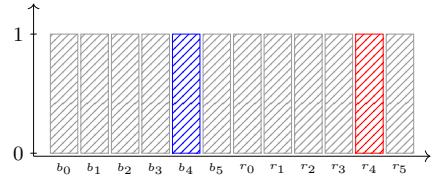

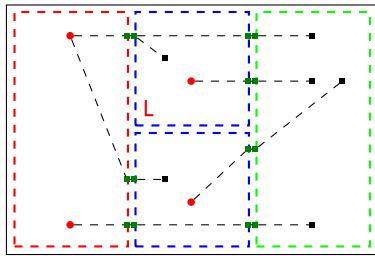

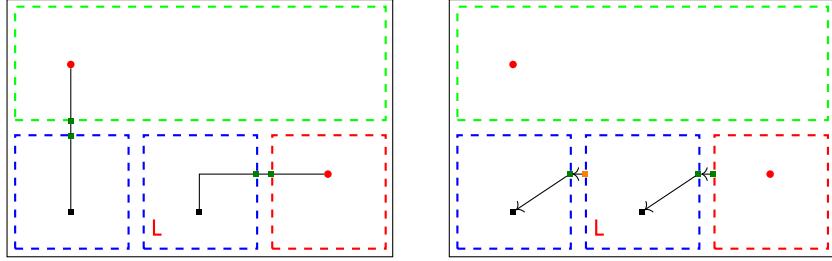

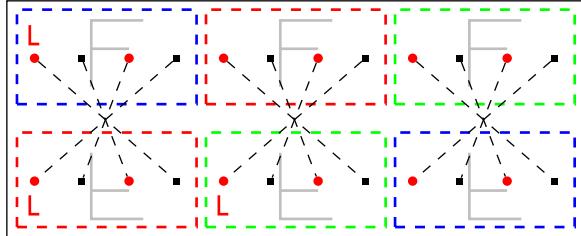

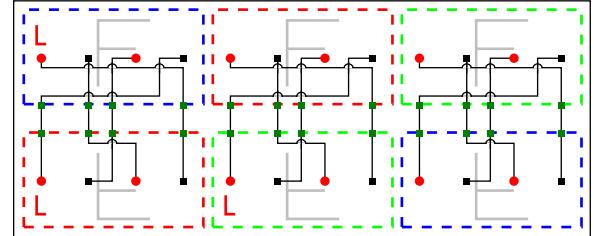

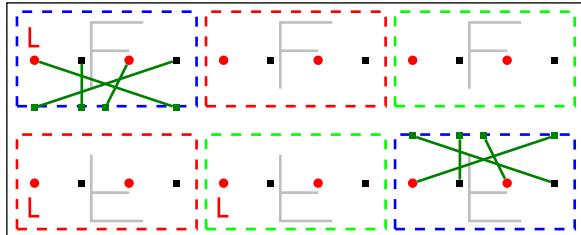

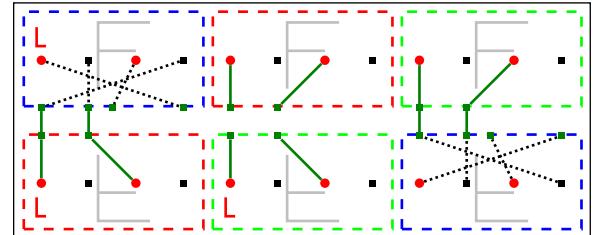

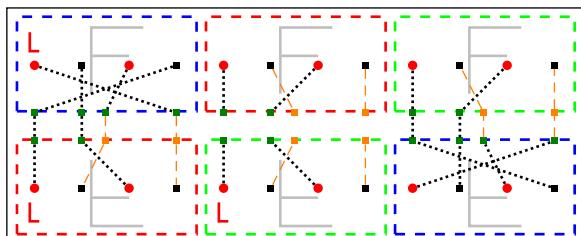

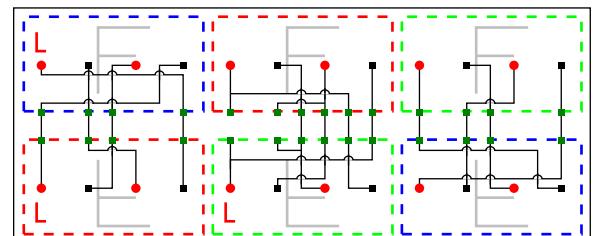

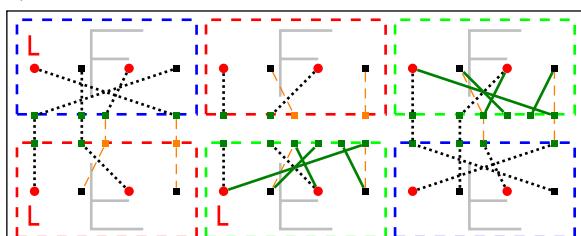

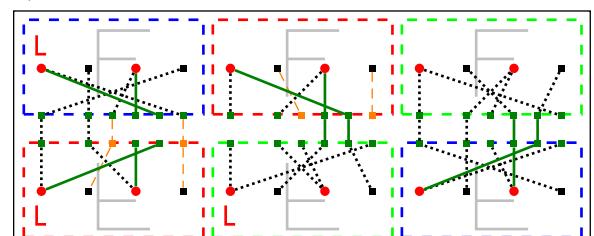

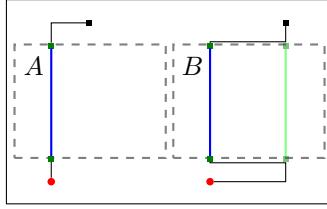

**Figure 3.2:** Weakness of Algorithm 2:  $(M, c)$  is induced by a complete graph with seven vertices and unit weights. Delay weights are indicated by the blue node labels and  $\mu = 1$ . Algorithm 2 might start with the minimum-length Steiner tree on the left. Then the algorithm will cut the edge incident to  $r$  and reconnect the sub-arborescence resulting possibly in the solution in the middle. On the right the result from our improved algorithm is shown.

---

**Algorithm 3:** Modifying Step 2 of Algorithm 2

---

**Step 2 (split into branching):**

Traverse  $A_0$  bottom-up. For each traversed edge  $(v, z) \in E(A_0)$  consider  $A_z := (A_0)_z$ : If  $W_{A_z} > 0$  and

$$\sum_{e=(p,q) \in E(A_z)} \frac{2W_{(A_z)_q}(W_{A_z} - W_{(A_z)_q})}{W_{A_z}} c(e) + \frac{D_{A_z}}{W_{A_z}} \leq \frac{\mu}{2} (C_{A_z} + c(v, z)) + \frac{D_{A_z}}{\mu}, \quad (3.4)$$

remove  $(v, z)$  creating a new arborescence  $A_z$ .

---

**Lemma 3.5.** Let  $A' \in \mathcal{A}$  be an arborescence that was cut off in Algorithm 3 and let  $e_{A'}$  be the incoming edge in the root of the arborescence  $A'$  which was deleted during this step. Then the corresponding terminals in  $T_{A'}$  can be connected to the root  $r$  with total cost at most

$$\left(1 + \frac{\mu}{2}\right) (C_{A'} + c(e_{A'})) + \left(1 + \frac{1}{\mu}\right) D_{A'}.$$

□

After the original Step 2 of Algorithm 2, it is clear that for all edges  $(r, x) \in \delta_{A_0}^+(r)$  of the root component the total delay weight  $W_{(A_0)_x}$  is at most  $\mu$ . We show that this also holds after the modified Step 2 in Algorithm 3. However, the analysis is more complicated and uses the following two functions.

**Definition 3.6.** Let  $\mu > 0$  and  $X^\mu := \{(a, b, c) \in (\mu, 2\mu) \times (0, \mu)^2 : c \leq a - b < \mu\}$ . We define the functions  $f, g: X^\mu \rightarrow \mathbb{R}$  as

$$f(a, b, c) := \frac{2(a - c)c}{a} - \frac{\mu}{2} + \left(\frac{1}{a} - \frac{1}{\mu}\right) \cdot \frac{1}{\frac{1}{a-b} - \frac{1}{\mu}} \cdot \left(\frac{\mu}{2} - \frac{2((a-b)-c)c}{a-b}\right)$$

$$g(a, b, c) := \frac{2(a - c)c}{a} - \frac{\mu}{2} + \left(\frac{1}{a} - \frac{1}{\mu}\right) \cdot \frac{1}{\frac{1}{a-b} - \frac{1}{\mu}} \cdot \frac{\mu}{2}.$$

**Lemma 3.7.** For all  $(a, b, c) \in X^\mu$ ,  $f(a, b, c) \leq 0$  and  $g(a, b, c) \leq 0$ .

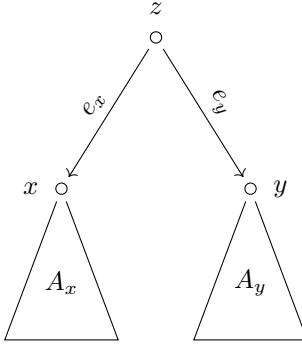

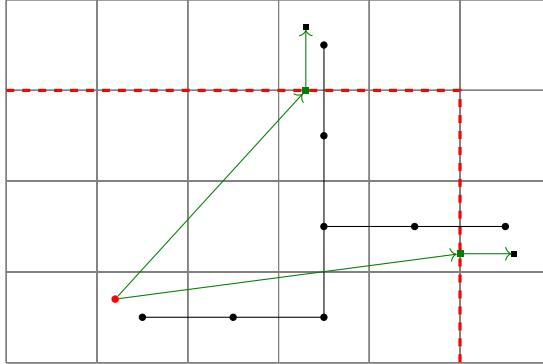

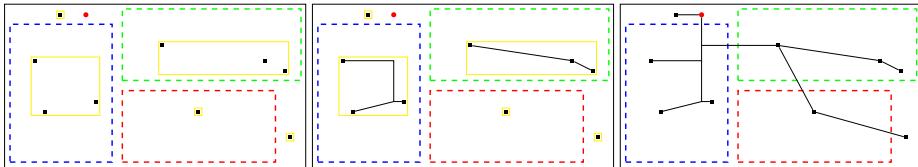

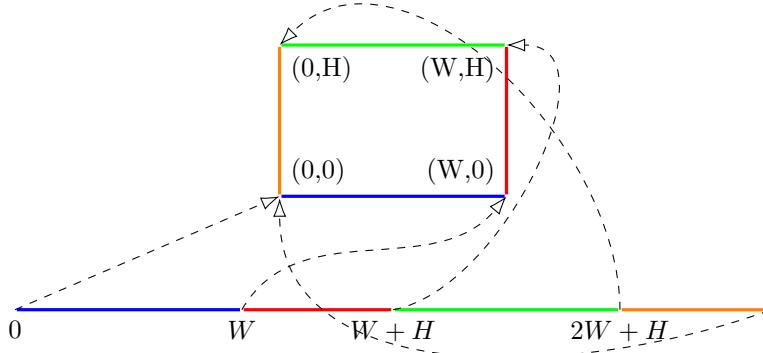

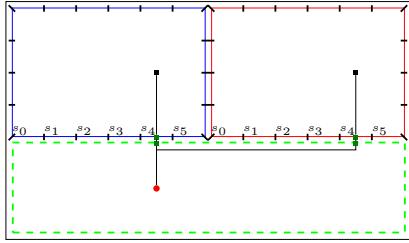

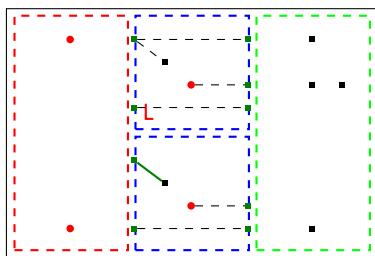

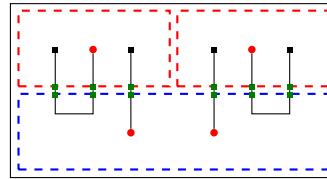

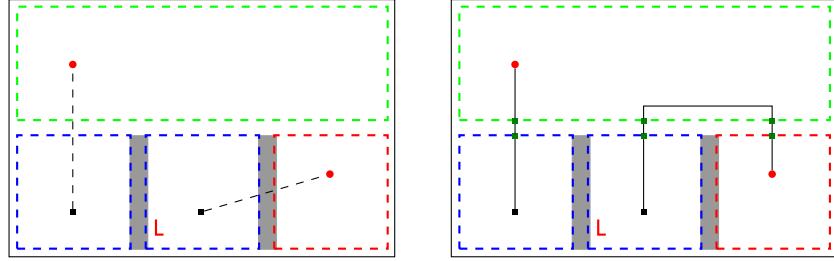

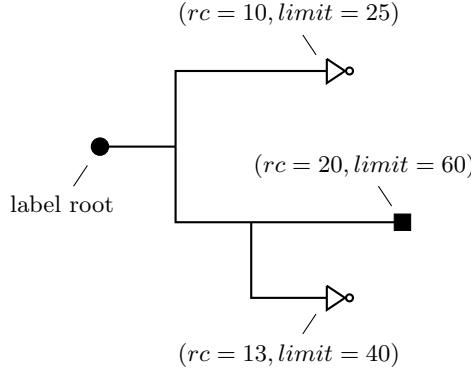

**Figure 3.3:** Setting in the proof of Lemma 3.8 if  $z$  is a Steiner vertex (Case 2).

A proof of Lemma 3.7 based on algebraic transformations can be found in the appendix of [FHS23](#).

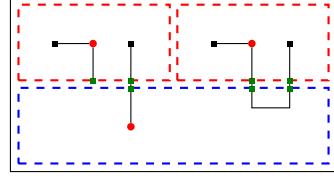

**Lemma 3.8.** *After cutting off sub-arborescences with Algorithm 3, every child  $x \in \Gamma_{A_r}^+(r)$  of  $r$  in the remaining root component  $A_r := (A_0)_r$  satisfies  $W_{(A_r)_x} \leq \mu$ .*

*Proof.* Assume the opposite would be true. Let  $z$  be a vertex in  $A_r - r$  such that the weight of the sub-arborescence  $A_z := (A_r)_z$  exceeds  $\mu$  and the weight of every child arborescence  $(A_z)_x$  is at most  $\mu$  for all edges  $(z, x) \in \delta_{A_z}^+(z)$ . We distinguish two cases:

Case 1:  $z$  is a terminal: Then  $z$  is also a leaf and the left-hand side of (3.4) simplifies to

$$\frac{1}{W_{A_z}} D_{A_z} \leq \frac{1}{\mu} D_{A_z}$$

since  $A_z$  does not contain any edges. But then  $A_z$  would have been cut-off in Step 2, a contradiction.

Case 2:  $z$  is a Steiner vertex: Then  $z$  has two outgoing edges  $e_x := (z, x), e_y := (z, y) \in \delta_{A_z}^+(z)$  as shown in Figure 3.3. A single outgoing edge would contradict the choice of  $z$ . With  $A_x := (A_z)_x$  or  $A_y := (A_z)_y$  this implies  $0 < W_{A_x}, W_{A_y} \leq \mu$ . If  $W_{A_x} = \mu$ , Lemma 3.4, (3.2) shows that  $A_x$  satisfied the bound (3.4) when it was considered in Step 2 and would have been cut off. Analogously,  $W_{A_y} \neq \mu$ . Thus,  $W_{A_x}, W_{A_y} < \mu$ . Since (3.4) does not hold for  $A_x$ , we get (by transforming its negation)

$$\underbrace{\left( \frac{1}{W_{A_x}} - \frac{1}{\mu} \right)}_{>0} D_{A_x} > \sum_{e=(u,v) \in E(A_x)} \left( \frac{\mu}{2} - \frac{2(W_{A_x} - W_{(A_x)_v})W_{(A_x)_v}}{W_{A_x}} \right) c(e) + \frac{\mu}{2} c(e_x).$$

Combining this with the analogue inequality for  $A_y$  and using  $D_{A_z} = D_{A_x} + D_{A_y}$ , we

get

$$\begin{aligned}

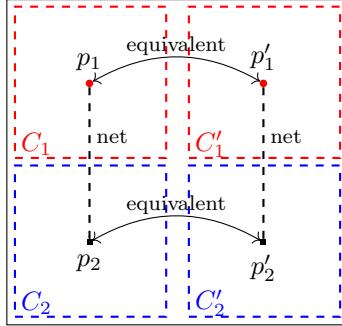

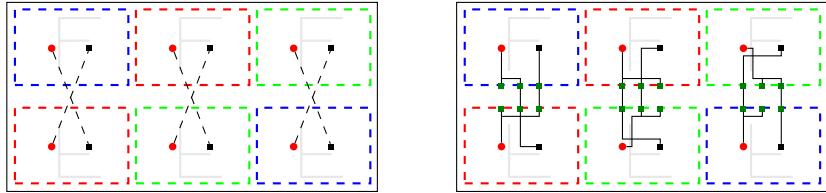

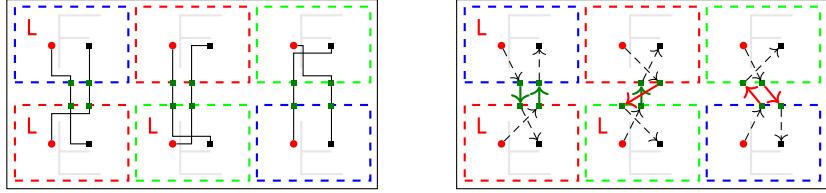

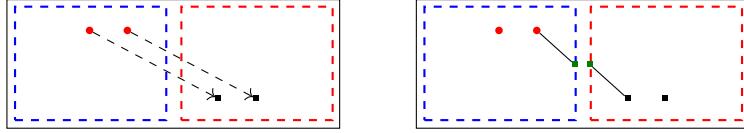

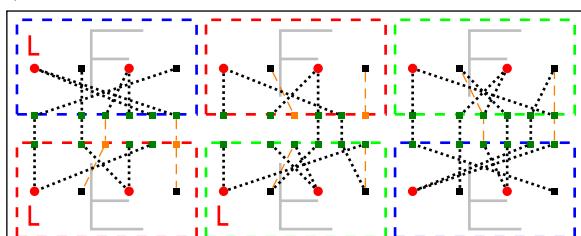

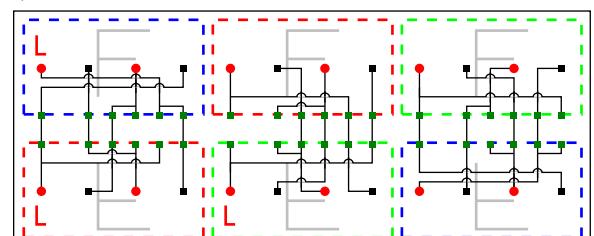

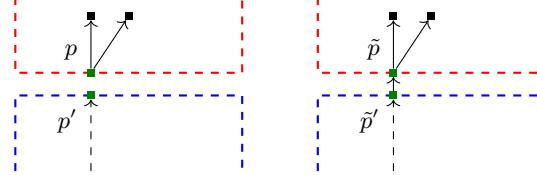

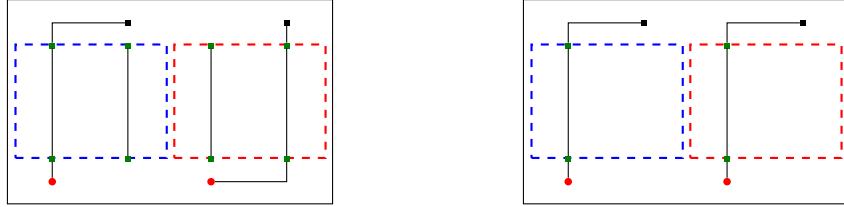

& \underbrace{\left( \frac{1}{W_{A_z}} - \frac{1}{\mu} \right)}_{<0} D_{A_z} \\