# Global Timing Optimization in Chip Design

DISSERTATION

ZUR

Erlangung des Doktorgrades (Dr. rer. nat.)

DER

MATHEMATISCH-NATURWISSENSCHAFTLICHEN FAKULTÄT

DER

Rheinischen Friedrich-Wilhelms-Universität Bonn

Vorgelegt von

SIAD DABOUL

AUS

LIPPSTADT

BONN, JANUAR 2021

Angefertigt mit Genehmigung der Mathematisch-Naturwissenschaftlichen Fakultät der Rheinischen Friedrich-Wilhelms-Universität Bonn

| 0                  | Herr Professor Dr. Stephan Held<br>Herr Professor Dr. Jens Vygen |

|--------------------|------------------------------------------------------------------|

| Tag der Promotion: | 19. März 2021                                                    |

| Erscheinungsjahr:  | 2021                                                             |

# Acknowledgements

Throughout the writing of this work, I have received a large amount of support and assistance by many people. First and foremost, I would like to thank my supervisors Professor Dr. Stephan Held and Professor Dr. Jens Vygen for their support, feedback, ideas and collaboration on many aspects of this thesis.

The working conditions at the Institute for Discrete Mathematics are excellent. I want to thank especially Prof. Dr. Bernhard Korte for creating this environment and for establishing the cooperation with IBM more than 30 years ago. This partnership has provided a lot of benefits for both sides and will hopefully do so for many years to come.

I am grateful to my colleagues Tilmann Bihler, Dr. Ulrich Brenner, Josefine Foos, Dr. Anna Hermann, Dr. Dirk Müller, Bento Natura, Stefan Rabenstein, Benjamin Rockel, Dr. Daniel Rotter, Pietro Saccardi, Dr. Rudolf Scheifele, Dr. Ulrike Schorr and Dr. Jannik Silvanus. Discussing some difficult problem or just meeting up for a coffee was always a pleasure. I want to thank Benjamin Rockel and Dr. Daniel Rotter in particular for proofreading a preliminary version of this work and for providing valuable comments and remarks.

Furthermore, I would like to express my gratitude to several current and former IBM employees for providing help and sharing their knowledge. In particular William Dougherty, Harald Folberth, Michael Kazda, Lakshmi Reddy, Gregory Schaeffer, Friedrich Schroeder, Alex Suess and Cindy Washburn.

Lastly, I thank my family for their encouragement and support in the time of working on this thesis.

# Contents

| 1        | Intr                        | coduction                                                             | 1  |

|----------|-----------------------------|-----------------------------------------------------------------------|----|

| <b>2</b> | 2 Preliminaries             |                                                                       | 7  |

|          | 2.1                         | Timing Analysis                                                       | 9  |

|          | 2.2                         | The Linear Timing Model                                               | 10 |

|          | 2.3                         | Elmore Delay                                                          | 11 |

|          | 2.4                         | Higher Order Delay Models                                             | 12 |

|          | 2.5                         | Power Analysis                                                        | 13 |

|          | 2.6                         | Timing Metrics                                                        | 14 |

|          | 2.7                         | An Overview                                                           | 16 |

| 3        | Interconnect Optimization 1 |                                                                       | 19 |

|          | 3.1                         | Previous Work                                                         | 20 |

|          | 3.2                         | Global Routing                                                        | 21 |

|          | 3.3                         | Min-Max Resource Sharing                                              | 23 |

|          | 3.4                         | Topology Generation                                                   | 32 |

|          | 3.5                         | Buffering                                                             | 34 |

| 4        | Tin                         | ne-Cost Tradeoff Problems in Chip Design                              | 37 |

|          | 4.1                         | Previous Work                                                         | 38 |

|          | 4.2                         | Problem Formulation                                                   | 39 |

|          | 4.3                         | $V_{\rm t}$ Optimization Algorithm                                    | 40 |

|          | 4.4                         | Variants and Implementation                                           | 46 |

|          | 4.5                         | Experimental Results                                                  | 49 |

| <b>5</b> | The                         | eoretic Bounds for Time-Cost Tradeoff Problems                        | 57 |

|          | 5.1                         | Previous Work                                                         | 58 |

|          | 5.2                         | Results and Outline                                                   | 59 |

|          | 5.3                         | The Vertex Cover LP                                                   | 60 |

|          | 5.4                         | Rounding Fractional Vertex Covers in $d\mbox{-Partite Hypergraphs}$ . | 65 |

|          | 5.5                         | Inapproximability                                                     | 75 |

|          | 5.6                         | Reducing Vertex Deletion to Constant Depth                            | 79 |

|          | 5.7                         | Variants of the Time-Cost Tradeoff Problem                            | 83 |

|    | 5.8   | The Power Recovery Problem                                   | . 87  |

|----|-------|--------------------------------------------------------------|-------|

| 6  | Gat   | ate Sizing                                                   |       |

|    | 6.1   | Previous Work                                                | . 90  |

|    | 6.2   | Gate Sizing as a Resource Sharing Problem                    | . 91  |

|    | 6.3   | Comparison to the Projected Subgradient Method               | . 99  |

| 7  | Bon   | nRouteBuffer                                                 | 105   |

|    | 7.1   | Previous Work                                                | . 106 |

|    | 7.2   | Problem Formulation                                          | . 108 |

|    | 7.3   | An Oracle for the Cost-Based Buffered Steiner Tree Problem . | . 112 |

|    | 7.4   | Improvements                                                 | . 120 |

|    | 7.5   | Comparison to Rotter                                         | . 126 |

|    | 7.6   | Global Interconnect Optimization Flow                        | . 128 |

|    | 7.7   | Experimental results                                         | . 129 |

| 8  | Sun   | nmary                                                        | 133   |

| Bi | bliog | graphy                                                       | 135   |

| No | otati | on                                                           | 149   |

ii

#### Chapter 1

# Introduction

During the design of a computer chip, numerous objectives compete against each other. First and foremost, we have the specified clock frequency. The chip only works correctly if implicit interconnect delay bounds are met. Other objectives include the minimization of wiring space usage, power consumption and placement space usage. Individual objectives are often contrary, for example fast realizations of combinatorial cells are available with the drawback of a substantial power consumption. Solving these tradeoff problems is the main topic of this thesis.

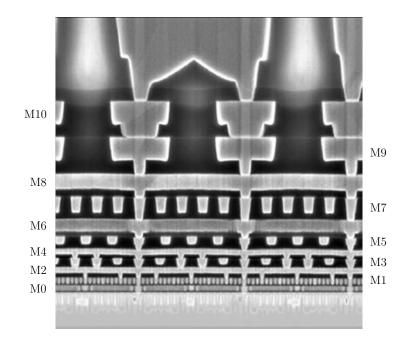

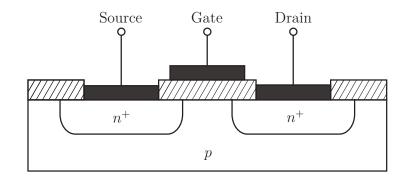

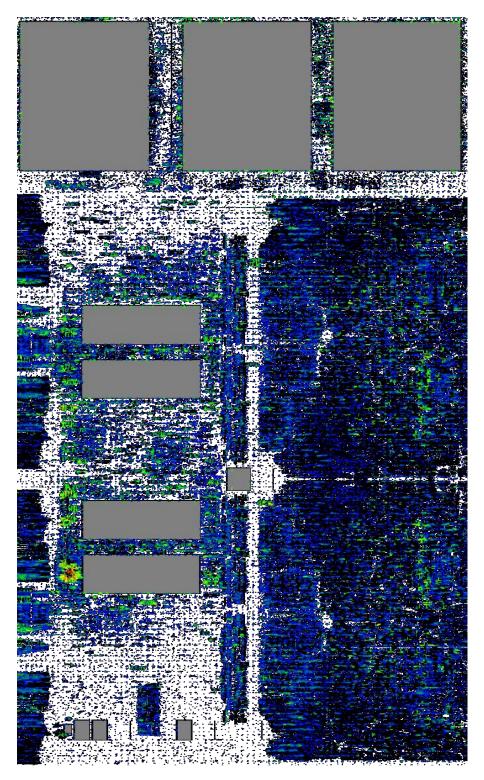

On a fundamental level, a computer chip consists of transistors. These tiny devices allow a current to flow depending on the voltage at their gate contact. By adjusting transistor materials in the manufacturing process, switching voltages  $(V_t)$  of combinatorial cells can be greatly improved at the cost of increased power consumption. The individual transistors only implement a simple Boolean function, but when connected to each other in the right way they realize a complex circuit. Modern chips have many wiring layers with various options to select wire widths and spacings. These choices heavily influence resource consumption and signal delays. Figure 1.1 shows the metal stack of a chip in the 10nm technology node. Higher layers have a significantly larger cross-section for individual wiring segments. This corresponds to a lower electrical resistance and, thus, reduced signal delays. However, due to large spacings only few wires can be packed on upper layers. Hence, individual nets compete for limited routing resources. The main goal of the design process is to reach the specified timing constraints while not overusing any of the available resources.

The availability of extremely thick wiring layers and fast transistors allows most signal constraints to be met at the cost of high resource usage. We can also see timing constraints as an available resource which is overused if the constraints are violated. Therefore, the design process is inherently a *resource-sharing* problem, in which the available resources are distributed to meet timing constraints. An essential objective of this problem is to find a

Figure 1.1: A cross section of the metal stack in the Intel 10nm technology node. Annotations on the left and right side name the routing layers. Layers ending in an odd digit are vertical, i.e., the routing preference direction is orthogonal to the cross section. Layers ending in even digits are horizontal. One can see that the individual layers have highly asymmetric routing space consumption characteristics. Image from: Intel, [Aut+17].

solution that does not overuse any resource. If such a solution does not exist the maximum overuse should be minimized. In contemporary industrial design flows, this problem has often been solved heuristically, for example by starting with a solution of low resource usage and to rely on postoptimization to resolve timing problems [Li+12].

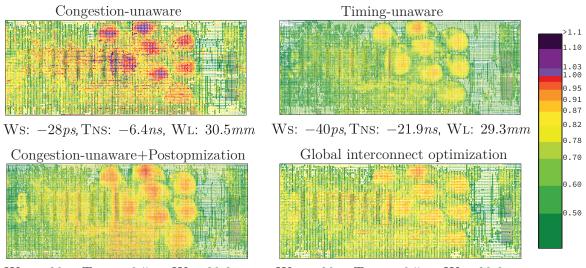

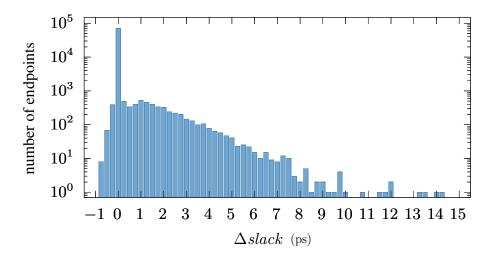

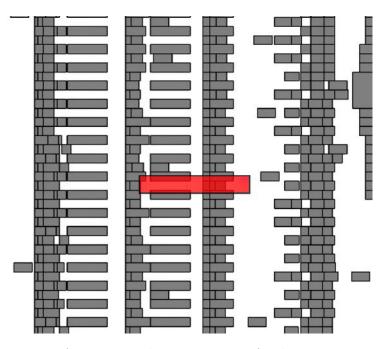

For the case of interconnect optimization, an example of this approach is depicted in Figure 1.2. Here, we show the resource usage, as indicated by the wiring length (WL) and the routing space consumption (visualized by the edge colors), compared to the achieved timing. As timing constraints usually cannot be satisfied in early design phases, the infeasibility is given by the worst slack (WS). The worst slack measures the maximum time by which a signal misses its required time of arrival. As it depends only on a single failing signal path it can be easily affected by perturbations of the netlist. Therefore, we also compute the total negative slack (TNS), which does not only measure the worst path but sums the slacks of a larger set of timing endpoints. Negative values of WS and TNS indicate that signals arrive too late. The timing-unaware solution, which only aims to minimize the routing resource usage, obtains a good wiring length but significantly violates the timing constraints. Therefore, heuristic postoptimizations lead to a suboptimal

WS: -29ps, TNS: -8.5ns, WL: 30.3mm WS: -29ps, TNS: -6.5ns, WL: 29.8mm

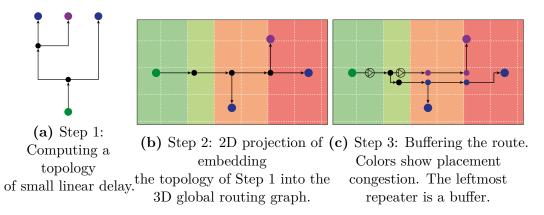

Figure 1.2: An example of four different design flows. The respective images highlight the routing resource usage of the computed interconnect. A red or purple color indicates infeasible resource usage. If resource capacity constraints are ignored, the computed result is not feasible, as can be seen in the top left picture. If timing constraints are ignored, the chip has a poor design frequency as indicated in the top right. A classic approach postoptimizes this solution, resulting in the solution shown in the bottom left. A new approach, combining timing constraints and resource usage minimization is shown in the bottom right.

solution at significantly increased resource usage and a large wiring length.

In this thesis, we aim at solving the interconnect optimization problem comprehensively. By balancing global timing, routing, placement, and power constraints in a global model, we obtain solutions which outperform the classic approach in both resource usage and timing quality.

An important special case of the *resource sharing* problem arises when we only have two resources: timing and cost. Consider the problem of selecting a solution in a discrete set of delay/cost alternatives for the vertices of an acyclic directed graph. If both delay and cost functions are separable, this is the well-known discrete *time-cost tradeoff* problem. Due to its numerous applications, it was already considered in the context of planning and scheduling more than 60 years ago [KW59]. However, on the positive side not much is known. In practice this problem is mostly solved by heuristics.

Our main contributions are as follows. For the time-cost tradeoff problem in chip design, we present a new implementation of a primal-dual  $V_t$  optimization algorithm. Instead of requiring separable delay constraints as in previous approaches, it only has mild assumptions on the delay model. The new

assumptions mostly hold in practice, even when computing non-linear delays with an industrial sign-off timer. This approach allows us to achieve leakage reductions of up to 8% on netlists that were pre-optimized by one of the most successful algorithms for gate sizing and  $V_t$  assignment [RSR16a]. Our algorithm simultaneously computes an a posteriori lower bound which shows that we solve some of the instances almost optimally. After global routing the reduction grows up to 34% without changing any footprints.

The  $V_t$  assignment problem with separable delays directly corresponds to the discrete time-cost tradeoff problem in directed graphs. If d is the maximum number of vertices in any path, our practical algorithm yields a d approximation. Previously, Svensson [Sve12] showed that for general instances with unbounded values of d no constant factor approximation exists if we assume  $P \neq NP$  and the Unique Games Conjecture holds. The latter conjecture was proposed by Khot in 2002 [Kho02]. Since then, many strong inapproximability results have been found under this conjecture. For example, it implies that vertex cover is NP hard to approximate up to a factor  $2 - \epsilon$  [KR08]. Therefore, the simple greedy algorithm is essentially best possible.

For the discrete time-cost tradeoff problem, we devise an improved algorithm with a guarantee of  $\frac{d}{2}$ . We achieve this by reformulating the problem to a vertex cover problem in *d*-partite hypergraphs. For this more general problem, the approximation ratio of our new algorithm is slightly better than  $\frac{d}{2}$ , which is asymptotically best possible under the Unique Games Conjecture and  $P \neq NP$ . We also study the inapproximability of the time-cost tradeoff problem and show that no better approximation ratio than  $\frac{d+2}{4}$  is possible, again assuming the Unique Games Conjecture and  $P \neq NP$ . Therefore, we settle the approximability of this problem up to a factor of less than 2.

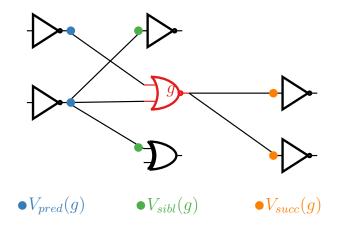

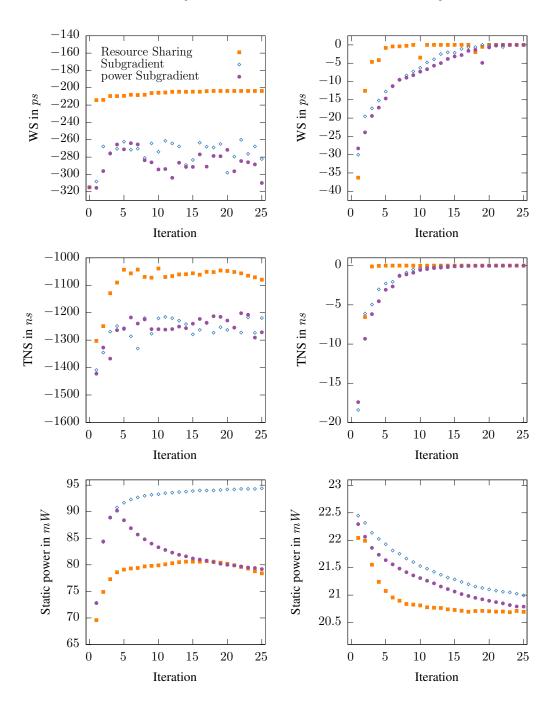

We then focus on the gate sizing problem. It is similar to the time-cost tradeoff problem but optimizes a more involved timing function, which is not linear but only posynomial. Schorr [Sch15] presented a resource-sharing formulation for the gate sizing problem in her dissertation. We give a new runtime analysis for the resource sharing algorithm applied to gatesizing, resolving small inaccuracies in the previous proof. Furthermore, Schorr [Sch15] compared the subgradient method to the resource sharing algorithm. We extend her analysis for the case where an additional power constraint is added to the problem. Our findings indicate that a power constraint significantly improves the subgradient method. However, even with the new model the resource sharing algorithm converges faster.

Besides, we present a practical implementation of the resource sharing algorithm for gate sizing with heuristic modifications. We compare our new implementation with the state-of-the-art algorithm of Reimann et al. [RSR16a]. On all designs our algorithm obtains similar or better power savings while drastically reducing runtime. On the larger testcases the speedup is between a factor of 6 and 10.

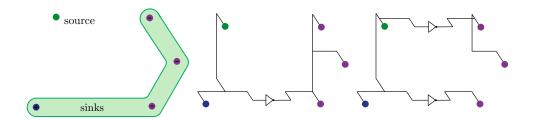

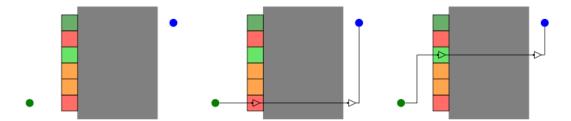

Finally, we consider the buffering problem. In this problem the interconnect for all nets should be computed. Simultaneously, repeating gates need to be inserted to strengthen electrical signals. We build on the resource sharing formulation for this problem given by Rotter [Rot17]. On the theoretic side, we modify the model by using a path based formulation for timing proposed by Hähnle [Häh15]. This simplifies the implementation and does not lead to worse results as our experiments show. We also point out that the problem formulation of Rotter relied on a rough subdivision of the chip to select buffer positions. In practice this could lead to high movements in the subsequent legalization step. We change the problem formulation to account for this and present a practical algorithm to obtain solutions which can be easily legalized.

Rotter gave a first implementation of his algorithm, but acknowledged that it still had several shortcomings which prevented its application in practice [Rot17]. The new implementation is now robust enough to be used in an industrial environment. It resolves all major issues of the previous implementation and subsequently outperforms a state-of-the-art design flow in almost all metrics, including netlength, power, congestion and timing. We also implement speedups that reduce the runtime by up to 70%.

Our ambition is to solve the resource sharing problems globally instead of relying on local optimization. All three described algorithms are now integrated in the design flow of our industrial partner IBM where they replaced their previous counterparts. Therefore, the new optimization flow now uses a uniform objective which encompasses all important design aspects.

This thesis is structured as follows. In Chapter 2 we give an overview of the chip design process and describe how the timing of a chip is modeled. The design process step in which Steiner trees are packed in a grid graph to find an interconnect solution obeying routing capacities is called *Global Routing*. As this step is of major importance for obtaining an algorithm that optimizes both timing and resource usage, we dedicate a separate chapter to it: Chapter 3.

In Chapter 4 and 5 we show how to solve the time-cost tradeoff problem in theory and practice. The following Chapter 6 discusses the gate sizing problem. The final Chapter 7 is dedicated to BONNROUTEBUFFER.

## Chapter 2

## Preliminaries

The mathematical problems discussed in this thesis arise in the context of chip design. We will use this chapter to familiarize the reader with fundamental concepts of the aforementioned design process. To this end, we assume fundamental graph theoretic notions as introduced in the book of Korte and Vygen [KV11]. For a comprehensive overview on the topic, we also recommend the habilitation thesis by Vygen [Vyg01] or the dissertation of Held [Hel08].

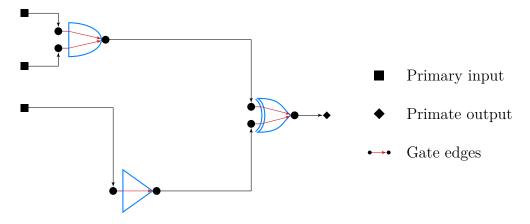

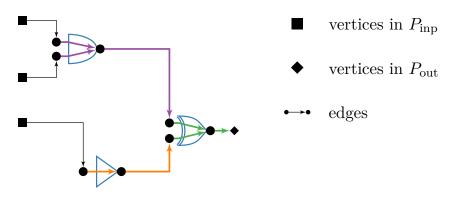

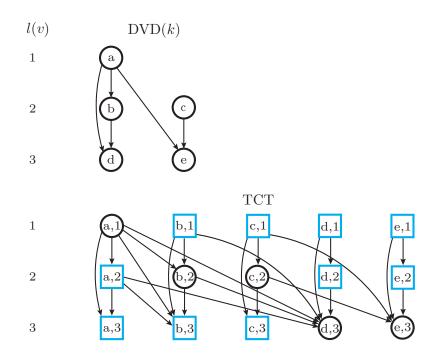

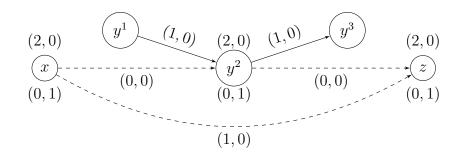

In a computer chip, information is transmitted by electrical signals. These can be separated into data and clock signals, of which this thesis only considers data signals. Unlike clock signals, which are cyclic signals used to control the chip, data signals are generally the result of some Boolean computation. A data signal starts in either a primary input or a register, traverses combinatorial gates and ends in a primary output or a register. This gives rise to the fine timing graph, a non-empty directed acyclic graph D = (V, E). The vertices correspond to pins. More formally, we have  $V(D) = P_g \cup P_{inp} \cup P_{out}$ . The sets  $P_{inp}$  and  $P_{out}$  correspond to starting points and endpoints of signals respectively. As described earlier, these pins are precisely given by register inputs or outputs and primary inputs or outputs. The remaining pins  $P_g$  are given by pins of combinatorial gates. The timing graph of a circuit is sketched in Figure 2.2. An edge in the timing graph is present if and only if a signal passes along the corresponding pins.

At every point in time, the electrical signal can be measured and corresponds to a certain voltage between 0 and  $V_{dd}$ . Here,  $V_{dd}$  is the operating voltage of the chip. Technically, it is possible that a chip has multiple voltage domains with different values of  $V_{dd}$ .

When the signal passes through the chip, the exact characteristics of the signal propagation are given by solutions to differential equations. Unfortunately, for the general case no closed form of these solutions is known. As solving differential equations is a costly operation, approximations are used. If the signal at a pin changes, its voltage either transitions from 0 to  $V_{dd}$  or vice versa. Therefore, we distinguish between rising and falling signals. A sample

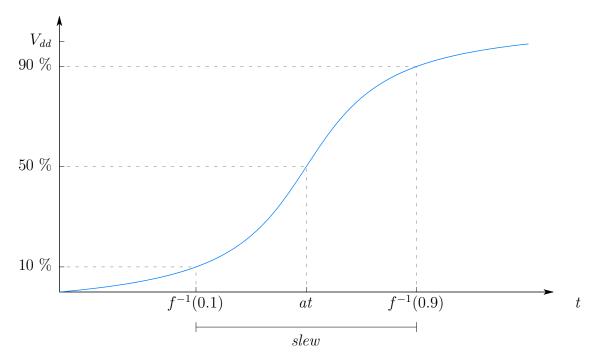

**Figure 2.1:** A sample voltage curve f(t) of a rising signal. The *slew* is the time the signal takes to rise from  $\frac{1}{10}V_{dd}$  to  $\frac{9}{10}V_{dd}$  and the arrival time *at* is the time the signal takes to rise from the ground voltage to  $\frac{1}{2}V_{dd}$ .

voltage curve of a rising signal is given in Figure 2.1. We define the time of arrival corresponding to the signal as the point in time in which the voltage surpasses  $\frac{1}{2}V_{dd}$ . The *slew* of the signal is the timespan in which the signal rises from  $\frac{1}{10}V_{dd}$  to  $\frac{9}{10}V_{dd}$ . Usually, not only constraints on the time of arrival of a signal are imposed, but also bounds on the slew have to be obeyed.

Before we describe the static timing analysis, a model to obtain signal delays for every logic path, we quickly describe the pins of combinatorial cells  $P_g$ . These vertices  $P_g \subset V$  in the timing graph correspond to input and output pins of a collection of gates  $\mathcal{G}$ , which are implementations of Boolean functions. An illustration of a simple timing graph with the corresponding gates is given in Figure 2.2. Instead of building every gate separately on a transistor level, these gates are typically selected from a technology-dependent library of books  $\mathcal{B}$ . This library contains a set of pre-designed layouts for at least a complete set of logical functions such that every Boolean function can be expressed. The books may differ in their size, number of transistors and threshold voltages ( $V_t$  level), which influence the timing characteristics of the gate. An implementation that uses a larger number of transistors may be faster at the cost of more placement usage and power consumption. Again, we encounter a resource sharing problem that consists of selecting the right implementations such that timing constraints can be met while minimizing resource consumption.

Figure 2.2: An example of a timing graph. Blue gates indicate how the graph arises from the underlying chip.

An assignment of all gates to books  $\beta : \mathcal{G} \to \mathcal{B}$  is called technology mapping. If the assignment differs from the initial solution only in the size of the book and its threshold voltage (i.e., a gate is mapped to a possibly different implementation of the same logical function), we call  $\beta$  a *cell selection*. Even when only optimizing threshold voltages of the gates, finding a cell selection that minimizes power consumption is a difficult problem as we will see in Chapter 5. If we fix the technology mapping, we can assign every edge in the timing graph  $(v, w) \in E(D)$  some delay value delay<sub> $v,w</sub>(<math>\beta$ )  $\geq 0$ . For gate edges this value may be part of the library, but the delay of a gate edge usually does not only depend on the book of the corresponding gate, but also on that of adjacent ones.</sub>

## 2.1 Timing Analysis

If we fix the technology mapping  $\beta$  and delay values of every edge, we can use static timing analysis to compute the time it takes for a signal to traverse the timing graph. To this end, we assume that for all input ports  $p \in P_{inp}$ fixed arrival times  $\operatorname{at}(p) \in \mathbb{R}$  are known. These represent the time at which the signal arrives at these inputs. Similarly, the output ports  $p \in P_{out}$  have required arrival times  $\operatorname{rat}(p)$ , which represent the latest acceptable time at which the signal may arrive at these ports. For an inclusion-wise maximal path  $P \in \mathcal{P}$  in the timing graph, we can define its delay by

$$\operatorname{delay}(P) = \sum_{(v,w) \in E(P)} \operatorname{delay}_{v,w}(\beta).$$

It is easy to see that the timing constraints are satisfied, if and only if  $delay(P) \leq rat(t) - at(s)$  for every s-t path P in the timing graph. At first,

this description seems to be impractical due to the exponential size of  $|\mathcal{P}|$ , but we may always sample a violated path in polynomial time. Indeed, we will see in Section 3.3.3 that this formulation can be very useful.

One way to turn the path formulation into polynomial constraints is given by introducing arrival times. As the timing graph is acyclic, we can propagate the arrival times in topological order by setting

$$\operatorname{at}(w) := \max_{(v,w) \in E(D)} \operatorname{at}(v) + \operatorname{delay}_{v,w}(\beta).$$

Analogously we can propagate required arrival times in reverse topological order by setting

$$\operatorname{rat}(v) := \min_{(v,w) \in E(D)} \operatorname{rat}(w) - \operatorname{delay}_{v,w}(\beta).$$

Comparing the arrival times with the required arrival times shows us if the chip meets the timing requirements. For this, we define the *slack* of a pin  $p \in V(D)$ as

$$\operatorname{slack}(p) := \operatorname{rat}(p) - \operatorname{at}(p).$$

A major goal of timing optimization is to find a technology mapping that guarantees  $\operatorname{slack}(p) \ge 0$  for all pins  $p \in V(D)$ .

# 2.2 The Linear Timing Model

The delay of a wire segment increases roughly quadratically with its length. Thus, in particular on low layers, delays can quickly become prohibitive. In contrast, an optimally buffered point-to-point connection has roughly linear delay. A *buffer* is a gate which reinforces the electrical signal by repeating it. It can either implement the identity function or invert the electrical signals. An even number of inverting buffers can be used to ensure logical correctness of the chip. In early design stages, before buffers have been inserted, one usually linearizes delays.

In the linear timing model, all net edges  $(p,q) \in E(D)$  have a specific fixed delay

$$\operatorname{delay}_{p,q}(\beta) = d_{p,q}^{edge}.$$

Note that the delay does not depend on the technology mapping  $\beta$ . For a gate edge  $(v, w) \in E(D)$  of some gate  $g \in \mathcal{G}$  we have

$$\operatorname{delay}_{v,w}(\beta) = d_{\beta(g)}^{gate}.$$

In particular, the delay of the gate g does not depend on the mapping  $\beta(g')$  for

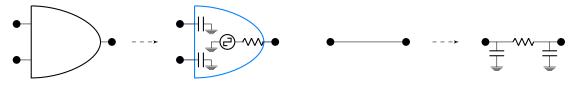

Figure 2.3: Transformation of a gate and a wire into an RC circuit.

$g \neq g' \in \mathcal{G}.$

#### 2.3 Elmore Delay

After buffer insertion a linear delay model is too optimistic. A pin of high capacitance has to be connected large gates in order to reach a reasonable timing. The Elmore delay model [Elm48] is significantly more accurate than the linear model but is still simple enough to be computed efficiently. It has the useful property that it is pessimistic, i.e., the real delay is never underestimated. Therefore, a solution that satisfied all timing constraints under Elmore delay is also feasible under more accurate models. However, it may use an excessive amount of inverters and too many routing resources.

Elmore delay is an RC delay model, it assumes that the interconnect is given by a network of resistors and capacitors. An approach by Fishburn et al. [FD85] transforms books and wiring segments into such a network. Here, a book  $b \in \mathcal{B}$  is characterized by four values: a size  $x_b$ , a base resistance  $\hat{r}_b$ , a base pin capacity  $\hat{c}_b$  and a base power factor  $\alpha_b$ . For a given  $b \in \mathcal{B}$  we now replace every input pin with a capacitor of a grounded capacity  $x_b\hat{c}_b$  and an ideal power source. We connect the power source to the output pin by a resistor of resistance  $\frac{\hat{r}_b}{x_b}$ . The power consumption of the book is given by  $\alpha_b x_b$ . To model wires we use a base resistance  $\hat{r}_w$  and a base capacitance  $\hat{c}_w$ . We insert a capacitor of capacity  $\frac{\hat{c}_w}{2}$  before and after the resistor of resistance  $\hat{r}_w$ . This transformation is illustrated in Figure 2.3.

We can now explain how the Elmore delay of an edge in the timing graph can be computed. For a gate edge  $(v, w) \in E(D)$  of a gate  $g \in \mathcal{G}$  we set

$$\operatorname{delay}(v, w) = \frac{\widehat{r_g}}{x_g} \operatorname{downcap}(w).$$

Here, downcap(w) computes the *downstream capacitance* of the pin w, this is the sum of all wire capacitances  $\widehat{c_w}$  of the Steiner tree connecting w to downstream gates and all input pin capacitances  $x_{g'}\widehat{c_{g'}}$  of these connected gates. For an edge (p,q) this Steiner tree represents the wiring that connects the vertices  $\delta_D^+(p) \cup \{p\}$ . We can give it a natural orientation by directing the

**Figure 2.4:** The shielding issue. The effective capacitance measured at the first resistor may be significantly smaller than  $\sum_{i=1}^{n} C_i$ .

edges from the logical source to the sinks. Therefore, it can be interpreted as a directed arborescence  $Y^p$ . Let Y[p,q] denote the unique p-q path in that arborescence. We can now set

$$\operatorname{delay}(p,q) = \sum_{e=(v,w)\in E(Y[p,q])} \widehat{r_e}\left(\frac{\widehat{c_e}}{2} + \operatorname{downcap}(w)\right)$$

In this formula downcap(w) is the sum of all wire and pin capacitances of the sub-arborescence rooted at  $w \in V(Y^p)$ . With a discrete library the sizes  $x_g$  are usually fixed, sometimes we relax the problem and allow the size to be within a specified region  $l_g \leq x_g \leq u_g$ .

We see that the delay of a path P can be written as

$$d(P) = \sum_{k=1}^{K} c_k \prod_{g \in \mathcal{G}} x_g^{b_{g,k}}$$

where  $c_k > 0, b_{g,k} \in \{-1, 0, 1\}$ . Functions of this form (even for general  $b_{g,k} \in \mathbb{R}$ ) are called *posynomial*. Posynomial functions can be turned into convex functions by a simple variable transformation [HH16].

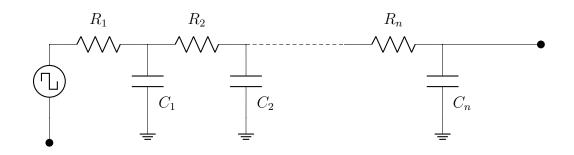

#### 2.4 Higher Order Delay Models

While the Elmore delay model can be computed efficiently, it is too inaccurate to be used in late stages of the design process. One reason is that it often significantly overestimates capacitances. A worst-case example is given by a path of n resistors of resistance  $R_1, \ldots, R_n$  where after every resistor i we insert an antenna of capacity  $C_i$ . This instance is depicted in Figure 2.4. According to the Elmore delay, we have a delay of  $R_1 \sum_{i=1}^n C_i$  at the first resistor. In reality, the downstream resistors shield away a major part of the capacitance that is near the end of the path. The effective capacitance  $\sum_{i=1}^{n} C_i^{effective}$  is the real capacitance visible at the first resistor (subtracting the capacitance that is shielded away by downstream resistors). More accurate delay models like RICE [RP94] approximately solve differential equations to determine these effective capacitance values. Current-based models as described by Croix et al. [CW03] are slightly less accurate but much faster and, therefore, commonly used.

#### 2.5 Power Analysis

While power was mostly a secondary objective in older technologies, it is becoming increasingly important as transistor sizes shrink. Modern chips have a huge power dissipation, which can even become the limiting design bottleneck.

The power consumption  $P_{total}$  depends on the technology mapping  $\beta : \mathcal{G} \to \mathcal{B}$ and on the interconnect. A part of this power consumption is a permanent leakage, which always occurs when the chip is powered on and is constant over time. We denote this by the *static power*  $P_{static}$ . The second part is the dynamic power  $P_{dynamic}$ . In our model the dynamic power consumption only occurs when the transistors switch and depends on the switching frequency  $\chi_g$  which can also depend on the specific usage of the chip. In addition to the selection of gates, nets that switch frequently should be as short as possible to minimize power dissipation. For simplicity, one usually assumes that these power functions are separable and can be computed by

$$P_{static}(\beta) = \sum_{g \in \mathcal{G}} \text{static_power}(\beta(g)),$$

$$P_{dynamic}(\beta) = \sum_{g \in \mathcal{G}} \text{dynamic_power}(\beta(g))$$

There are also other kinds of dynamic power, for example dynamic leakage. In practice, tight slew bounds make sure that our model is reasonably accurate. The interested reader is referred to the book chapter by Held and Hu for more details [HH16].

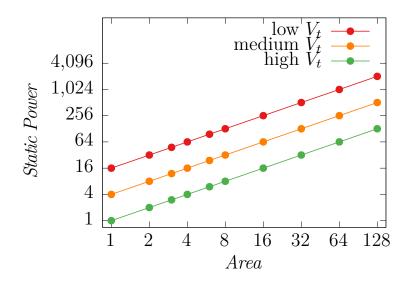

In the model by Fishburn et al. [FD85] a given gate  $g \in \mathcal{G}$  is assumed to have a continuous size  $x_g \in [L, U]$  such that its input capacitance is given by  $\hat{c}_g x_g$ . As explained previously, gates may also have different threshold voltages  $V_t$ . This can be achieved by using different substrates for manufacturing transistors. A lower threshold voltage increases the static power consumption and lowers the threshold at which the transistor can switch its state, lowering the delay. As there is usually a small discrete set of possible threshold voltages, we also speak of  $V_t$  levels.

A typical assumption is that the static power consumption of a gate is

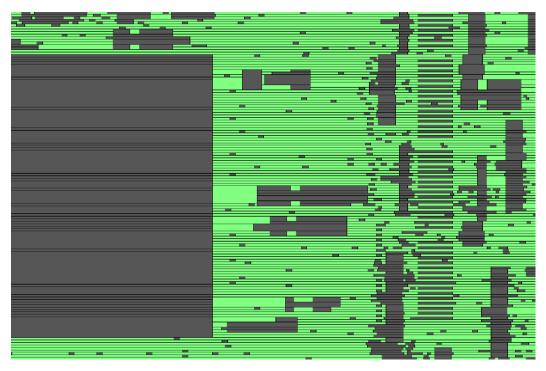

Figure 2.5: The cell library for an inverter as given in the ISPD 2013 contest. The axes are plotted logarithmically. The three different colors indicate different threshold voltages. High  $V_t$  corresponds to the slowest implementation of a fixed size, while low  $V_t$  is the fastest one.

proportional to the size of the gate and exponential in the  $V_t$  level of the gate. In contrast, the dynamic power consumption does not depend on the  $V_t$  level, which means that if for a given gate  $g \in \mathcal{G}$  the switching activity  $\chi_g$  is high it can be preferable to accelerate it by lowering the  $V_t$  level instead of increasing the size.

An example of a cell library is given in the ISPD 2013 contest for gate-sizing [Ozd+13]. Here, we have  $|X_g| = 10$  and for each of these sizes there are 3 possible  $V_t$  levels which gives us 30 possible implementations for the gate g. The library for an inverter is visualized in Figure 2.5.

## 2.6 Timing Metrics

In the previous sections, we explained how the timing of a chip can be modeled by introducing the timing graph and propagating arrival times. However, early in the design process not all timing constraints can be met. Instead of simply checking for feasibility, we try to find objective functions that can drive our optimization routines and penalize timing fails.

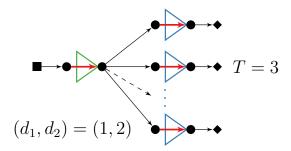

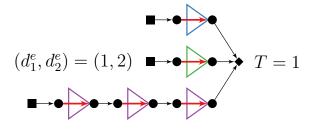

These metrics will allow us to compare different solutions, which do not completely meet all timing constraints. A different application is to use the timing metrics directly within optimization routines. A simple example is an algorithm by Kahng et al. [Kah+13] which counts the number of failing paths passing through a gate. We can evaluate the timing of the chip whenever we have delays available for all edges in the timing graph. This motivates the following definition. A *timing* solution is a tuple (D, d, T), where D is a timing graph,  $d : E \to \mathbb{R}_{\geq 0}$  is a delay function and  $T \geq 0$  is a deadline. In chip design T roughly corresponds to the cycle time at which the chip operates. A path P in the timing graph meets its timing constraints when the sum of its edge delays  $d(P) := \sum_{e \in E(P)} d(e)$  does not exceed T. Note that we can always assume that our delay constraints are encoded by such a deadline by inserting a super-source and a super-sink with arcs that correspond to the arrival times at the source pins and the required arrival times at the sink pins.

A timing metric is a map  $\tau : (D, d, T) \mapsto \tau(D, d, T) \in \mathbb{R}$  that assigns every timing solution a real number that should correspond to the timing feasibility of the instance. If D and T are fixed, we write  $\tau(d)$  for  $\tau(D, d, T)$ .

We will now give an overview of the most relevant timing metrics that are used in chip design. The most common is the *worst slack* timing metric

$$Ws(d) := \min_{P \in \mathcal{P}} \min \{T - d(P), 0\}.$$

The most important property of the worst slack metric is that it is nonnegative if and only if all timing constraints are met.

To define more advanced timing metrics we will introduce a couple of additional definitions. Recall that in the timing graph  $P_{inp} \subset V(D)$  are precisely the vertices without incoming edges, and  $P_{out} \subset V(D)$  the vertices without outgoing edges. For a fixed  $v \in V(D)$  we define the longest path through vby  $P_{max}(v) = \operatorname{argmax}_{P \in \mathcal{P}, v \in V(D)} d(P)$  and similarly for an edge  $e \in E(D)$  we define  $P_{max}(e) = \operatorname{argmax}_{P \in \mathcal{P}, e \in E(P)} d(P)$ . In case of a tie we choose the path lexicographically minimal with respect to some fixed order on the edges. Note that  $P_{max}$  can be evaluated in linear time by traversing the graph in topological and reverse topological order.

We can now define the total negative slack (also called "figure of merit" or "sum of negative slacks") timing metric. It is defined as

$$\operatorname{TNS}(d) := \sum_{v \in P_{out}} \min \Big\{ T - d(P_{max}(v, d)), 0 \Big\}.$$

One can easily see that  $TNS \leq WS$ .

A timing metric that was proposed by Reimann et al. [RSR16b], which we name "true total negative slack", is defined as follows: Let  $Q = \bigcup_{e \in E(D)} P_{max}(e, d)$ . Note that we may have |Q| < |E(D)|.

$$\mathrm{TTNS}(d) := \sum_{P \in Q} \min \Big\{ T - d(P), 0 \Big\}.$$

The TTNS can also be computed by traversing D in reverse topological order and for fixed  $v \in V(D)$  summing up the longest paths through every but the most critical edge in  $\delta^{-}(v)$ , where ties are broken arbitrarily. This yields a number  $\rho(v) \in \mathbb{R}$ . One can see that  $\text{TTNS}(d) = \text{TNS}(d) + \sum_{v \in V} \rho(v)$ . In particular we have  $\text{TTNS}(d) \leq \text{TNS}(d)$ .

A natural extension would be to sum up the slack of all paths. Namely we could compute the path total negative slack as follows

$$\operatorname{PTNS}(d) := \sum_{P \in \mathcal{P}} \min \Big\{ T - d(P), 0 \Big\}.$$

It turns out that there is a problem with this approach. It is easy to see by shifting the deadline by 1 that computing PTNS would also allow us to compute the negative number of violated paths:

$$NPATH(d) := -|\{P \in \mathcal{P} : d(P) > T\}|.$$

However, this is a hard problem as shown by Mihalák et al. [MSW14]:

**Theorem 2.1.** (Mihalák et al.) [MSW14] Given an acyclic digraph G = (V, E)and two vertices  $s, t \in V(G)$ , and some  $L \in \mathbb{R}$  then it is #P-complete to count the number of s-t paths of length at most L.

Here #P is a class of NP-hard counting problems (as these do not have a certificate of polynomial size). A trivial modification to the given reduction from the partition problem shows that unless P=NP there is no polynomial algorithm to compute PTNs or Npath. We remark that there is a polynomial algorithm to approximate NPATH, however its runtime of  $\mathcal{O}(mn^3\epsilon^{-1}\log n)$  does not seem practical [MSW14].

We end this section with the remark that a method was proposed by Kong [Kon02] to estimate the number of violated paths. It works by counting the number of all paths in a graph, which arises from the timing graph by deleting edges (p,q) if either slack $(p) \ge 0$  or slack $(q) \ge 0$ . This can be achieved by propagating the number of paths through a pin in both forward and backward topological order and by multiplying these values. However, this is not equivalent to computing NPATH. A counterexample was given by Daboul [Dab15].

#### 2.7 An Overview

Before we analyze some mathematical problems arising in the design process, it is helpful to roughly understand the physical design flow. As an input the flow starts with a pre-optimized logic description of the chip. Corresponding logic

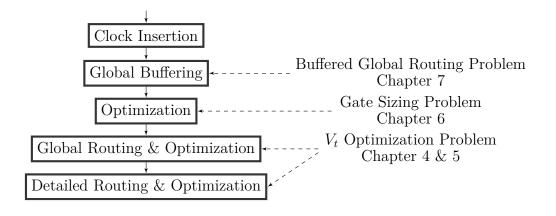

**Figure 2.6:** An excerpt of an industrial design flow proposed by Li et al. [Li+12]. On the right a list of mathematical problems discussed in this thesis is shown. Each problem is connected to its corresponding design steps.

gates are subsequently placed onto the chip area in the global placement step and optimized. An extended overview on a modern design flow was given by [Li+12]. A final step of the flow is to compute a *detailed routing*, which consists of wires connecting all gates on a chip. In addition to being overlap free, various other technological constraints have to be met. As it is infeasible to optimize at this level of accuracy, earlier steps of the flow use simple approximations that should make sure that a later detailed routing can still be found.

One way to ensure that enough wiring space is available to find a detailed routing is to coarsify the chip and to add capacity constraints on the estimated wiring in this simplified graph. The arising multicommodity flow formulation was first considered by [SK87] and the corresponding process of computing rough outlines for the later detailed wiring is called *global routing*.

In the clock network synthesis step thousands of clock trees have to be inserted. As the step can be very disruptive for the timing and wiring space usage of the chip, it is usually performed early in the design flow [Li+12]. For optimization before this step, the effects on the final result at the end of the flow can be marginal. Therefore, we will not focus much on the steps that precede clock network synthesis. Instead, our primary focus will be the global buffering step and subsequent optimization steps with and without a global routing.

A sketch of the design flow is given in Figure 2.6. In Chapter 7 we will discuss an algorithm for the global buffering problem. Our implementation of the resource sharing algorithm for gate sizing described in Chapter 6 is applied in the subsequent optimization step. After global routes have been computed, disruptive optimizations like gate sizing and buffering should be avoided. As  $V_t$

changes often leave gate footprints unchanged and do not require movements, the  $V_t$  optimization problem is well suited for applications after a global or even detailed routing. We will discuss it in Chapter 4 and 5. In the next chapter we familiarize the reader with the global routing problem and the resource sharing problem.

## Chapter 3

## **Interconnect Optimization**

This thesis deals with different resource sharing problems that occur in the chip design process. One fundamental resource is wiring space. To understand how we solve the overall problem of distributing routing and timing resources to individual connections, we first have to explain how this problem is to be solved if only a single resource, namely wiring space, is to be optimized.

The wiring on a chip is structured in *routing layers*, these have a preference direction that either allows vertical or horizontal wiring. The set of feasible wiring segments gives rise to the so-called *track graph*. This graph has an edge for every possible wiring segment that adheres to the preference direction of the particular layer. Vertical wire segments which allow switching between adjacent layers are called vias. Maximal subgraphs of wiring on a chip are named *routes*. Every route connects a logical source to a set of sinks. These pins connected by a route are called a *net* and denoted as  $N \in \mathcal{N}$ . The set of all nets  $\mathcal{N}$  is the *netlist*.

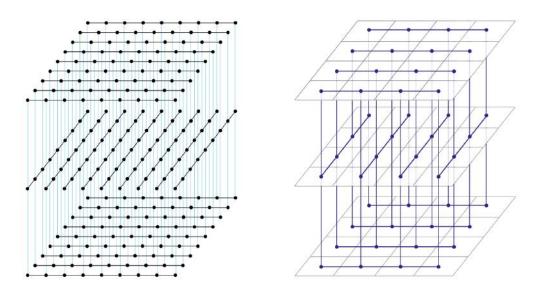

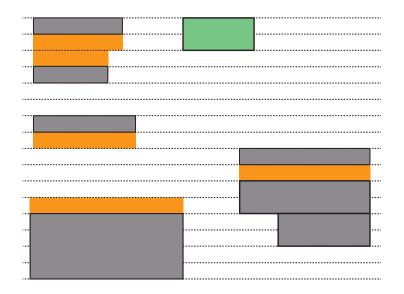

To ensure correct function, all wire segments have to be disjointly packed onto the chip while obeying various technology dependent spacing constraints. Optimizing a chip on this level of accuracy does not seem to be feasible with current technology and algorithms. Therefore, one usually relaxes the disjointness constraints. Instead, we coarsen the track graph into a grid graph and introduce capacity constraints on the edges. This process is illustrated in Figure 3.1.

In this thesis we will not consider detailed routing problems. Instead, we will always use the simplifying assumption that interconnects are computed in the global routing graph. However, especially for buffer insertion, we may compute routes that already connect to the specified metal shapes corresponding to a given net. For computing the routing space consumption, the route is then first projected into the global routing graph.

The global routing problem consists of finding a feasible fractional Steiner tree packing in this grid graph. Approximation algorithms for fractional multicommodity flows can be used to solve this problem and were already used in chip design over 30 years ago [SK87].

Since its initial formulation, many new constraints have been introduced to the global routing problem. Modern algorithms do not only solve a packing problem, but also optimize timing and perform simultaneous buffer insertion or placement optimization.

#### 3.1 Previous Work

As one of the most fundamental problems in chip design, the global routing problem has received a significant amount of attention in the past. The multicommodity flow formulation [SK87; CC91] has been extended to integrate net delay bounds and buffer insertion by [Alb+02], who presented a fully polynomial approximation scheme (FPTAS) for two-terminal nets.

A state-of-the-art algorithm for the classic global routing problem without timing constraints was given by Müller, Radke and Vygen [MRV11]. Their algorithm is based on a special multiplicative Lagrangean multiplier framework, called resource sharing.

Based on this algorithm Saccardi and Hähnle presented a novel approach which works with a rhomboidal subdivision of the chip [HS19]. By a structure theorem this allows them to compute global routes with a pin-level accuracy. This significantly improves the correlation with a later detailed routing.

Giving an exhaustive overview on previous global routing approaches would exceed the scope of this thesis. Many recent algorithms used in contests or during industrial design flows belong to a class of rip up and reroute heuristics. They often work on a 2d model of the routing graph and iteratively rewire the nets to reduce overuse of routing edges. Heuristically updating a cost function can work well in practice, but lacks a provable performance guarantee. Some notable examples are NTHU-Route [Cha+10], FastRoute [YYC09] and BoxRouter [Cho+09]. A different notable approach uses an integer program formulation for the global routing problem. The GRIP algorithm [WDL11] solves the overall integer program by solving smaller subinstances with a price-and-branch heuristic.

Integrating timing constraints into global routing has a rich history. First approaches by Huang et al. [Hua+93] used delay bounds to reject Steiner trees which do not meet these allocated budgets. This approach was later refined by Hong et al. [Hon+97] to path-based delay bounds. These approaches have several serious drawbacks. By seeing delay bounds as a hard constraint rather than a flexible resource, timing has to be significantly relaxed to prevent a couple of failing paths from dominating the overall solution. This weakness was first addressed by Vygen [Vyg04], who showed how to implement net based delay bounds into the resource sharing framework. The drawback is that only a subset of the timing constraints are considered.

More recently, Held, Müller, Rotter, Scheifele, Traub, and Vygen [Hel+17] showed how to integrate global static timing constraints into the resource sharing framework. This is the first solution which does not have the aforementioned problems of using fixed delay budgets or only considering a subset of the timing constraints. An alternative way of integrating path based timing constraints was given by Hähnle [Häh15].

Rotter [Rot17] presented a resource sharing formulation that combines routing and buffer insertion. He also implemented a heuristic oracle function that allowed him to obtain first promising results on practical instances. However, compared to the previous state-of-the-art design flow some metrics were still inferior. In Chapter 7 we will present a refined implementation which removes remaining drawbacks and significantly improves the design flow.

The algorithm of Rotter still used the classic routing graph description of [SK87; CC91] but heuristically connects global routes to pin positions before buffer insertion. It seems tempting to combine ideas of Rotter with the work of Saccardi and Hähnle [HS19] in the future to directly compute global routes with pin-level accuracy.

Previous approaches usually follow up a timing-unaware global routing step with a successive layer assignment and buffering step. An example is given by the CATALYST algorithm [WA04], which was the previous default method in the PDS-Turbo design flow [Li+12] used by IBM.

We will give a more detailed overview about previous work on the buffering problem in Chapter 7.

#### 3.2 Global Routing

For our applications, we will assume that the chip has a rectangular outline and a set of wiring layers. Let the *chip image* be defined as  $\mathcal{I} = \Box \times \{0, \ldots, Z\}$ , where  $\Box = [0, w] \times [0, h]$  is the area of the chip and Z is the number of routing layers. Layer '0' corresponds to the placement area  $\Box \times \{0\}$ . All repeaters and gates are inserted on this layer and the routing space has to be accessed by using vias.

Before we consider the step of buffer insertion, we will first explain how the global routes can be computed. Therefore, assume for the moment that all gates are part of the input and only a global routing should be computed for the nets. In addition to the global routing graph, we are given a set  $\mathcal{T}$  of *wire types*. In conjunction with an axis-parallel line segment  $I \subset \mathcal{I}$ , a wire type  $\tau \in \mathcal{T}$  determines a space consumption, as well as electrical resistance and capacitance of the metal shape pair  $(I, \tau)$ . In practice, not all wire types can be used on every routing layer. This can be modeled by assigning the combination

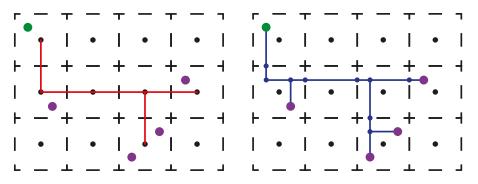

Figure 3.1: An illustration of the track graph and the corresponding global routing graph. On the left side, the track graph is shown. The edges of the track graph correspond to possible wiring segments on the chip. The right side shows a possible global routing graph. Instead of computing disjoint wiring segments, the global routing graph can be used to assign the individual nets to certain routing corridors. These only obey a capacity constraint on the total use of a global routing edge, which should assert that in the end a feasible solution can still be found. The vertical distance between two adjacent layers was artificially increased for better visibility.

an infinite resistance and capacitance.

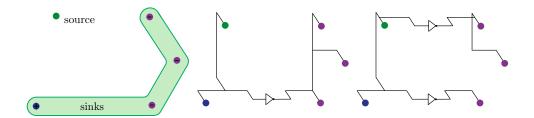

Each net  $N \in \mathcal{N}$  consists of a source pin  $s \in \Box \times \{0, \ldots, Z\}$  and a set of sink pins  $T \subset \Box \times \{0, \ldots, Z\}$ . In particular for non-linear timing models, the order in which sinks are connected to the root is essential.

A topology for a net N is an arborescence A rooted in s, such that T is the set of leaves. We require that the root has exactly one successor and all inner vertices have outdegree at most 2. This degree constraint is only for convenience, as we can always reduce degrees by introducing additional vertices to the arborescence.

An *(embedded) Steiner tree* for a net N is a topology A together with a map into the chip image  $p: V(A) \to \mathcal{I}$ . p has to satisfy p(s) = s, p(t) = t for the source s and any sink  $t \in T$ . We further require that the image (p(v), p(w)) for edges  $(v, w) \in E(A)$  are either of length 0 or axis-parallel routing stick figures, i.e., they have to correspond to an edge in the global routing graph.

With these definitions we can define a first version of the Global Routing problem, by looking for an (embedded) Steiner tree for every net  $N \in \mathcal{N}$ , such

1

that overall capacity bounds are obeyed. When it is clear from the context that we describe an embedded Steiner tree in the chip image, we sometimes omit "embedded" and simply write Steiner tree to simplify notation.

Problem 1: Traditional Global Routing Problem

- **Input:** The global routing graph G, edge lengths  $l : E(G) \to \mathbb{R}_{\geq 0}$ , a netlist  $\mathcal{N}$ , wire types  $\mathcal{T}$  and a routing space oracle usg :  $E(G) \times \mathcal{T} \to \mathbb{R}_{\geq 0}$ .

- **Task:** Compute Steiner trees  $(A_N, p)$  for all  $N \in \mathcal{N}$  with  $p(V(A_N)) \subseteq E(G)$ with wire type assignments  $\tau_e \in \mathcal{T}$  for all  $e \in E(A_N)$ . For a global routing edge  $\{i, j\} \in E(G)$  let  $Q_{i,j}^N := \{(v, w) \in E(A_N) | (p(v), p(w)) = (i, j)\}$  be the edges mapped to it by  $A_N$ . The Steiner trees have to obey capacity constraints

$$\sum_{N \in \mathcal{N}} \sum_{e \in Q_{i,j}^N} \operatorname{usg}(p(e), \tau_e) \le 1 \quad \text{ for all } \{i, j\} \in E(G).$$

The objective is to minimize netlength:  $\sum_{N \in \mathcal{N}} l(E(A_N))$ .

The main goal of this Chapter is to first introduce the min-max resource sharing problem, which allows us to solve the fractional relaxation of the traditional global routing problem up to the Steiner ratio. Finally, we will focus on the more general problem of simultaneous routing and buffering.

#### 3.3 Min-Max Resource Sharing

We follow the definitions introduced in [MRV11] and use the following problem formulation.

**Problem 2:** Min-Max Resource Sharing Problem

- **Input:** A finite set  $\mathcal{R}$  of *resources*, a finite set  $\mathcal{C}$  of *customers*. For every customer  $c \in \mathcal{C}$  a convex set  $B_c$ . For all customer resource pairs  $(c, r) \in \mathcal{C} \times \mathcal{R}$  a convex usage function  $usg_{c,r} : B_c \to \mathbb{R}_{\geq 0}$ .

- **Task:** Compute a vector of solutions  $b = (b_c)_{c \in \mathcal{C}}$ , such that  $b_c \in \mathcal{B}_c$  for all  $c \in \mathcal{C}$ . The objective is to minimize the maximum resource consumption

$$\lambda(b) = \max_{r \in \mathcal{R}} \sum_{c \in \mathcal{C}} \operatorname{usg}_{c,r}(b(c)).$$

The intuition behind this definition is that a set of limited resources is to be distributed to the customers. A solution  $b \in B_c$  decides how much of a given resource the customer uses. In our applications the sets  $B_c$ , which are also called *blocks*, will always be compact. Therefore, the optimum solution is well defined. The sets of possible solutions  $B_c$  for a customer can be exponentially or even infinitely large; therefore they may only be given implicitly.

To be able to solve the resource sharing problem, we assume that *oracle* functions are given. For a customer  $c \in C$  an oracle function  $f_c : \mathbb{R}_{\geq 0}^{\mathcal{R}} \to B_c$  is an approximate minimizer of the weighted resource minimization problem. Formally, we assume that there is a constant  $\sigma \geq 1$ , such that

$$y^{\top} f_c(y) \le \sigma \inf_{b \in \mathcal{B}_c} \sum_{r \in \mathcal{R}} y_r \operatorname{usg}_{c,r}(b)$$

for all  $y \in \mathbb{R}_{\ge 0}^{\mathcal{R}}$ .

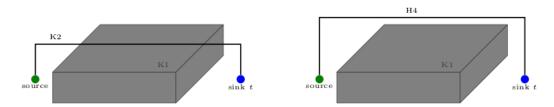

This generalization of the multicommodity flow problem allows us to see the fractional relaxation of the traditional global routing problem from a different perspective. We consider the nets  $\mathcal{N} =: \mathcal{C}$  as customers of a resource sharing problem. The feasible solutions are given by the convex hull of all feasible Steiner trees for the net. We introduce a resource for every edge in the global routing graph and a netlength resource; thus  $\mathcal{R} = E(G) \cup \{\text{netlength}\}.$

The usage function  $usg_{N,e}$  specifies how much the wiring segments of a Steiner tree  $A_N$  with given wire code assignment consume from the global routing edge  $e \in E(G)$  relative to its capacity. By performing a binary search, we may assume that we know the best possible netlength in form of a budget. This directly corresponds to a resource which measures how much the budget is violated. In the next section, we will give an outline of an algorithm that can solve the resource sharing problem if appropriate oracle functions are known.

Due to its general formulation, the resource sharing problem is well suited for its application in chip design. Numerous objectives can be encoded by defining appropriate resources. By focusing on relative resource consumptions it also provides a natural way to compare design objectives that have different units.

#### 3.3.1 The Resource Sharing Algorithm

In this section we will describe the algorithm of Müller, Radke, Vygen [MRV11] to solve the aforementioned resource sharing problem. To this end, assume that we are given an instance of the resource sharing problem and oracle functions for each customer. The main idea is to use a multiplicative update scheme which will generate the costs to use in our oracle function. The pseudocode of it is given as Algorithm 3.1.

The most important step of the algorithm is the exponential price update  $\operatorname{price}(r) \leftarrow e^{\gamma \xi \operatorname{usg}_{c,r}(b)} \cdot \operatorname{price}(r)$ . Rip up and reroute heuristics for the global routing problem usually use similar exponential price updates to avoid overuse of routing edges. However, the algorithm shows that this price update can

#### Algorithm 3.1: Resource Sharing Algorithm by [MRV11].

**Input:** An instance of the (fractional) min-max resource sharing problem. Oracle functions  $f_c$  for all  $c \in \mathcal{C}$ .  $\gamma > 0, t \in \mathbb{N}$ . **Output:** A solution  $x_c = \sum_{b \in B_c} x_{c,b}b$  for all  $c \in C$ . 1 for  $r \in \mathcal{R}, c \in \mathcal{C}, b \in B_c$  do price $(r) \leftarrow 1, X_c \leftarrow 0, x_{c,b} \leftarrow 0$  $\triangleright$  Initialization step  $\mathbf{2}$ 3 for  $p = 1 \dots t$  do for  $c \in \mathcal{C}$  s.t.  $X_c < p$  do  $\mathbf{4}$  $b \leftarrow f_c(\text{price})$  $\mathbf{5}$  $\xi \leftarrow \min\{p - X_c, \min\{1/\operatorname{usg}_{c,r}(b) : \operatorname{usg}_{c,r}(b) > 0, r \in \mathcal{R}\}\}$ 6  $x_{c,b} \leftarrow x_{c,b} + \xi, X_c \leftarrow X_c + \xi$  $\mathbf{7}$ for  $r \in \mathcal{R}$  do 8 9 10 for  $c \in C, b \in B_c$  do  $x_{c,b} \leftarrow x_{c,b}/t$  $\triangleright$  Scale the solution by 1/t11

be done in a way that provably converges. A main result of [MRV11] is the following theorem.

**Theorem 3.1** (Müller, Radke, Vygen [MRV11]). For any  $\omega > 0$ , Algorithm 3.1 can be used to compute a solution to the min-max resource sharing problem with approximation ratio  $\sigma(1+\omega)$  in runtime  $\mathcal{O}(\theta(|\mathcal{C}|+|\mathcal{R}|) \log |\mathcal{R}|(\log \log |\mathcal{R}|+\omega^{-2}))$ . As above  $\sigma$  is the approximation guarantee of the oracle functions and  $\theta$  the time to evaluate an oracle function.

Let  $\lambda^*$  denote the optimum maximum resource usage of the given instance. In practice, we usually have  $\frac{1}{2} \leq \lambda^* \leq 2$ , as otherwise the instance is either easy to solve or completely infeasible. If we use this assumption, the analysis of the resource sharing algorithm yields a slightly better runtime of  $\mathcal{O}(\theta(|\mathcal{C}| + |\mathcal{R}|) \log |\mathcal{R}| \omega^{-2})$ . The main problem with this is that the runtime is still linear in the number of resources  $|\mathcal{R}|$ . In Section 3.3.3 we will encounter a resource sharing problem with an exponential number of resources. An important indicator to estimate the hardness of a resource sharing problem is the problem width. It is defined to be the worst possible overuse of a resource. More precisely

$$\Lambda = \sum_{c \in \mathcal{C}} \max\{1, \sup_{r \in \mathcal{R}, b \in B_c} \operatorname{usg}_{c,r}(b)\}.$$

For the traditional global routing problem, it is reasonable to assume that  $\Lambda = \mathcal{O}(|\mathcal{N}|)$ , as a single net certainly can be accommodated in any global routing edge. Müller, Radke and Vygen give the following useful bound, that allows problem formulations with exponentially many resources.

**Theorem 3.2** (Müller, Radke, Vygen [MRV11]). Let  $0 < \delta, \delta' < 1$ . Given an instance of the min-max resource sharing problem with  $\lambda^* \leq 1$ , we can compute  $a (\sigma(1+\delta) + \frac{\delta'}{\lambda^*})$  approximation in time  $\mathcal{O}(\sigma\theta \log |\mathcal{R}|\Lambda(\delta\delta')^{-1})$ .

The above algorithm can be used to solve the fractional min-max resource sharing problem. For the classic global routing problem, this yields a convex combination of Steiner trees for each net. As the discrete variant of the global routing contains the edge disjoint Steiner tree packing problem in grid graphs, we cannot hope for good algorithms to solve it. However, Müller Radke and Vygen show that rounding every net to a solution randomly, depending on its weight in the convex combination, yields a good solution. More formally, they show the following theorem.

**Theorem 3.3** (Müller, Radke, Vygen [MRV11]). Consider values  $x_{c,b}$  computed by Algorithm 3.1. After scaling, we have  $\sum_{b\in B_c} x_{c,b} = 1$ . If we randomly round the solution by choosing solution b with probability  $x_{c,b}$ , we obtain solutions  $\hat{b}_c$  for all  $c \in C$ . Let  $\lambda = \max_{r\in\mathcal{R}} \sum_{c\in C} \sum_{b\in B_c} x_{c,b} usg_{c,r}(b)$ . Let  $\hat{\lambda} = \max_{r\in\mathcal{R}} \sum_{c\in C} usg_{c,r}(\hat{b}_c)$ . For  $r \in \mathcal{R}$  let  $\rho_r := \max\{usg_{c,r}(b)/\lambda | b \in B_c, c \in C, x_{c,b} > 0\}$  and  $\delta > 0$ . Then  $\hat{\lambda} < \lambda(1 + \delta)$  with probability at least  $1 - \sum_{r\in\mathcal{R}} e^{-h(\delta)/p_r}$ , where  $h(\delta) := (1 + \delta) \ln(1 + \delta) - \delta$ .

This step is also called randomized rounding. In practice, it often leads to a good solution, which can be further refined by post-optimization. In the following sections, we will show how timing can be modeled within the resource sharing framework.

Depending on the resources in the problem formulation an oracle as used by the resource sharing algorithm may have different forms. For the timing constrained global routing problem we will discuss the oracle in Section 3.4. For the variant of simultaneous buffer insertion the oracle will be explained in Section 3.5.

#### 3.3.2 Arrival Time Customers

In this section we will present an approach by Held, Müller, Rotter, Scheifele, Traub, and Vygen [Hel+17] which extends the classic global routing resource sharing formulation to incorporate timing constraints. Let D be the timing graph as defined in Chapter 1. As before, we assume that input ports  $p \in P_{inp}$ with arrival times  $\operatorname{at}(p) \in \mathbb{R}$  are given. Similarly, the output ports  $p \in P_{out}$ have required arrival times  $\operatorname{rat}(p)$  and timing may be propagated by  $\operatorname{at}(w) = \max_{(v,w)\in E(G)}\operatorname{at}(v) + \operatorname{delay}_{v,w}$  and  $\operatorname{rat}(v) := \min_{(v,w)\in E(G)}\operatorname{rat}(w) - \operatorname{delay}_{v,w}$ . Our goal is to add resources and customers such that the resource usage is  $\leq 1$  if and only if all timing constraints are satisfied.

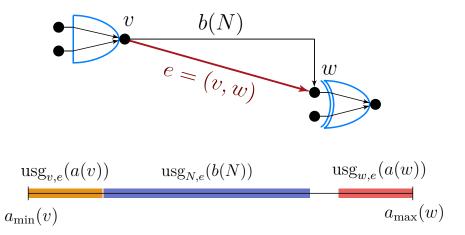

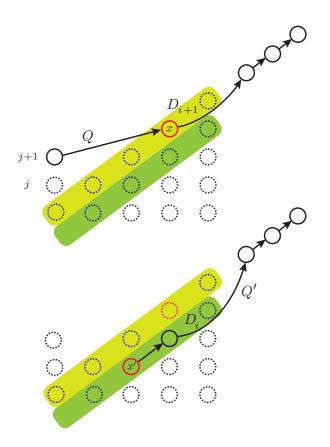

Figure 3.2: A visualization of the resource usage associated to a computed interconnect solution b(N) and the choice of arrival times on the start and endpoints. By assigning a later arrival time to w we could free up usage of the resource and compensate for a slow solution b(N). However, we simultaneously increase the usage of succeeding edge delay resources.

As a first step, we compute intervals of possible arrival times for all pins of the timing graph. These are given by lower and upper bounds  $d_{\rm lb}: E(D) \to \mathbb{R}_{>0}$ ,  $d_{\rm ub}: E(D) \to \mathbb{R}_{>0}$ , such that  $0 < d_{\rm lb}(e) \leq {\rm delay}_e(b(N)) \leq d_{\rm ub}$ . Here,  $\operatorname{delay}_{e}(b(N))$  denotes the delay along timing edge  $e \in E(D)$  for a given Steiner tree b(N) of a net  $N \in \mathcal{N}$ . In practice, we can use the fastest possible wire type and the best possible routing layers to compute lower bounds on the delay. As we usually do not allow arbitrary detours, upper bounds on the delay can be derived. The practical performance can be significantly improved if these lower and upper bounds are close and several ways exist to further improve them. We will not discuss the details in this thesis but refer the interested reader to [Hel+17]. By propagating these lower and upper bounds, we can compute intervals  $B_v = [a_{\min}(v), a_{\max}(v)]$ , for all  $v \in V(D)$ . Every feasible solution for all nets  $b(N) \in B_N$  will correspond to choices for arrival times  $a(v) \in B_v$ . Note that for input ports  $p \in P_{inp}$  we always have  $a_{\min}(p) = a_{\max}(p) = at(p)$ . Similarly, output ports  $p \in P_{out}$  satisfy  $a_{\min}(p) = a_{\max}(p) = rat(p)$ . We extend the resource sharing formulation of the classic global routing problem by adding arrival time customers for every vertex in the timing graph, i.e.,  $\mathcal{C} = \mathcal{N} \cup V(D)$ . The corresponding block of a customer  $v \in V(D)$  is given by  $B_v$ . We extend the set of resources by adding a delay resource for every edge in the timing graph, i.e.,  $\mathcal{R} = E(G) \cup E(D) \cup \{\text{netlength}\}$ . It remains to define the corresponding usage functions of a timing edge  $e = (v, w) \in e(D)$ . The resource will be used by the nets  $N \in \mathcal{N}$  and the arrival time customers  $v, w \in V(D)$ . Finally, we

define the following usage functions:

$$\operatorname{usg}_{v,e}(a(v)) := \frac{a(v) - a_{\min}(v)}{a_{\max}(w) - a_{\min}(v)}$$

$$\operatorname{usg}_{N,e}(b(N)) := \frac{\operatorname{delay}_e(b(N))}{a_{\max}(w) - a_{\min}(v)}$$

$$\operatorname{usg}_{w,e}(a(w)) := \frac{a_{\max}(w) - a(w)}{a_{\max}(w) - a_{\min}(v)}.$$

The construction is visualized in Figure 3.2. We will now argue why this usage functions correctly translates timing constraints into resource consumption. All timing constraints can be met if and only if for all  $v \in V(D)$ , one can find arrival times  $a(v) \in [a_{\min}(v), a_{\max}(v)]$ , such that  $a(v) + \text{delay}_e(b(N)) \leq a(w)$  for all  $e = (v, w) \in E(D)$ . Recall that we fix the arrival time intervals for primary inputs and outputs. Fix an arbitrary edge  $e = (v, w) \in E(D)$ . The usage of the corresponding edge delay resource is satisfied if and only if the following holds.

$$\begin{aligned} & \operatorname{usg}_{v,e}(a(v)) + \operatorname{usg}_{N,e}(b(N)) + \operatorname{usg}_{w,e}(a(w)) \leq 1 \\ \Leftrightarrow & \frac{a(v) - a_{\min}(v)}{a_{\max}(w) - a_{\min}(v)} + \frac{\operatorname{delay}_{e}(b(N))}{a_{\max}(w) - a_{\min}(v)} + \frac{a_{\max}(w) - a(w)}{a_{\max}(w) - a_{\min}(v)} \leq 1 \\ \Leftrightarrow & \operatorname{usg}_{v,e}(a(v)) + \operatorname{delay}_{e}(b(N)) \leq a(w) \end{aligned}$$

This proves that the construction indeed works and a solution which does not overuse any delay resource corresponds to obeying global timing constraints. It is left to explain how these arrival times can be computed during the resource sharing algorithm, i.e., to give oracle functions. For this, notice that the weighted usage function

$$\sum_{e \in E(D)} \operatorname{price}(e) \cdot \operatorname{usg}_{v,e}(a(v))$$

is a separable function which is linear in a(v). Therefore, a minimizer can be found by evaluating it at the interval borders  $\{a_{\min}(v), a_{\max}(v)\}$ . This approach is not very stable and arrival times can oscillate a lot. To improve stability and the rate of convergence, [Hel+17] propose to update the solution of arrival time customers more often. This does not affect the convergence guarantee of the overall resource sharing algorithm and can be done efficiently as [Hel+17] show. For the details of this update, we refer the reader to [Hel+17]. We will now show an alternate way of modeling timing resources in the resource sharing framework.

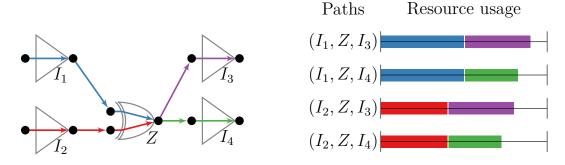

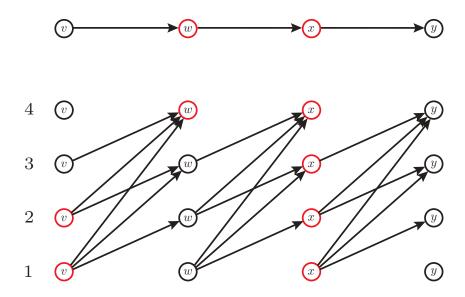

Figure 3.3: An illustration of timing path resources. The sample chip has 4 timing paths, each of which corresponds to an individual resource. The net customers which contain a given edge in a timing path will consume from the associated path resource.

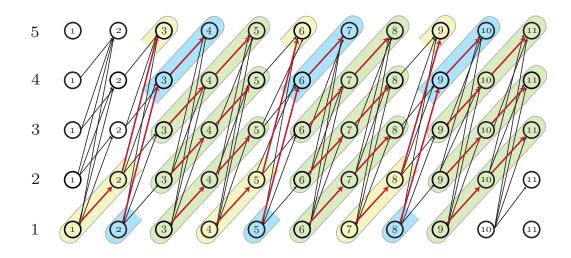

#### 3.3.3 Timing Path Resources

A natural way to model timing is to add an individual constraint for every path  $P \in \mathcal{P}(D)$  in the timing graph D. Here,  $\mathcal{P}(D)$  denotes the set of all inclusion-wise maximal paths in D. This directly corresponds to a resource sharing formulation, in which we introduce an additional resource for every such path. In the classic global routing problem, the resource set would be then given by  $\mathcal{R} = E(G) \cup \mathcal{P}(D) \cup \{\text{netlength}\}$ . For an s-t path P in the timing graph, let  $e \in E(P)$  be an edge corresponding to net  $N \in \mathcal{N}$ , the usage of this path resource by net customer N is simply given by

$$\operatorname{usg}_{N,P}(b(N)) = \frac{\operatorname{delay}_e(b(N))}{\operatorname{rat}(t) - \operatorname{at}(s)}$$

It is clear that in this way global timing constraints can be represented. However, at first this formulation does not look like it leads to a polynomial time algorithm. As shown in Theorem 3.2 the resource sharing algorithm can be analyzed in a way such that the dependency on the amount of resources is only logarithmic. It remains to show that we can compute timing prices for an edge in the timing graph, i.e., price(e) for  $e \in E(D)$  in polynomial time. For convenience, we define  $\omega_e := \text{price}(e)$ . Using the special structure of the resource sharing prices, Hähnle [Häh15] proved the following theorem. It shows that computing the prices only takes linear time.

**Theorem 3.4.** (Hähnle [Häh15; Dab+18a]) The edge weights  $\omega_e$  for  $e \in E(D)$ can be computed in each iteration of the resource sharing algorithm in time  $\mathcal{O}(|E(D)| + |V(D)|).$

#### Algorithm 3.2: Path Resource Timing Weights

Input: A timing graph *D*. Cumulative usages  $y_e$  for  $e \in E(D)$ .  $\gamma > 0$ . Output: Edge weights  $\omega_e$  for  $e \in E(D)$ . 1 for  $v \in P_{inp}, w \in P_{out}$  do 2  $\left[ \begin{array}{c} \omega_{\mathcal{P}_{[P_{inp},v]}} = 1 \leftarrow 1, \quad \omega_{\mathcal{P}_{[w,P_{out}]}} \leftarrow 1 \\ & & & & \\ \end{array}\right]$   $\rightarrow$  Initialization step 3 for  $v \in V(D)$  in topological order do 4  $\left[ \begin{array}{c} \omega_{\mathcal{P}_{[P_{inp},v]}} = \sum_{(u,v)\in E} \left(e^{\gamma \cdot y_{(u,v)}} \cdot \omega_{\mathcal{P}_{[P_{inp},u]}}\right) \\ & & & \\ \end{array}\right]$ 5 for  $v \in V(D)$  in reverse topological order do 6  $\left[ \begin{array}{c} \omega_{\mathcal{P}_{[v,P_{out}]}} = \sum_{(v,w)\in E} \left(e^{\gamma \cdot y_{(v,w)}} \cdot \omega_{\mathcal{P}_{[w,P_{out}]}}\right) \\ & & \\ \end{array}\right]$ 7 for  $e = (v, w) \in E(D)$  do 8  $\left[ \begin{array}{c} \omega_e = \exp(\gamma \cdot y_e) \cdot \omega_{\mathcal{P}_{[P_{inp},v]}} \cdot \omega_{\mathcal{P}_{[w,P_{out}]}} \\ & & \\ \end{array}\right]$   $\sim$  Compute  $w_e$ 9 return  $(\omega_e)_{e \in E(D)}$

**Proof** By the definition of the resource sharing algorithm, we have

$$\omega_e = e^{\gamma \xi \widehat{\mathrm{usg}}_{c,e}}.$$

Here,  $\widehat{\text{usg}}_{c,e}$  should denote the sum of all usages of timing edge  $e \in E(D)$  of previously computed solution vectors by the resource sharing algorithm. To ease notation, we write  $y_e := \xi \widehat{\text{usg}}_{c,e}$ . For a path, the total usage is then given as  $y_P := \sum_{e \in E(P)} y_e$ . We conclude that

$$\begin{split} \omega_e &= \sum_{P \in \mathcal{P}: e \in E(P)} \exp(\gamma \cdot y_P) \\ &= \sum_{P \in \mathcal{P}_{[P_{\mathrm{inp}}, v]}} \sum_{Q \in \mathcal{P}_{[w, P_{\mathrm{out}}]}} \exp\left(\gamma \cdot \sum_{f \in P \cup Q \cup \{e\}} y_f\right) \\ &= \exp(\gamma \cdot y_e) \cdot \underbrace{\left(\sum_{P \in \mathcal{P}_{[P_{\mathrm{inp}}, v]}} \exp\left(\gamma \cdot \sum_{f \in P} y_f\right)\right)\right)}_{=: \omega_{\mathcal{P}_{[P_{\mathrm{inp}}, v]}}} \\ &\cdot \underbrace{\left(\sum_{Q \in \mathcal{P}_{[w, P_{\mathrm{out}}]}} \exp\left(\gamma \cdot \sum_{f \in Q} y_f\right)\right)\right)}_{=: \omega_{\mathcal{P}_{[w, P_{\mathrm{out}}]}}} \\ &= \exp(\gamma \cdot y_e) \cdot \omega_{\mathcal{P}_{[P_{\mathrm{inp}}, v]}} \cdot \omega_{\mathcal{P}_{[w, P_{\mathrm{out}}]}}, \end{split}$$

where  $\mathcal{P}_{[P_{inp},v]}$  denotes the set of all paths from an input vertex to v and  $\mathcal{P}_{[v,P_{out}]}$  denotes the set of all paths from v to an output vertex. All variables

$\omega_{\mathcal{P}_{[P_{\text{inp}},v]}}, \omega_{\mathcal{P}_{[v,P_{\text{out}}]}}$   $(v \in V(D))$  can be computed in linear time by traversing D once in topological and once in reverse topological order. A possible implementation is presented as Algorithm 3.2.

#### 3.3.4 A first comparison

In the last two sections, we presented two ways to model timing in the resource sharing framework. The obvious question is which of the solutions should be preferred.

A general answer is unlikely to exist. However each formulation has its down and upsides. Timing path resources are very natural and easy to explain. They can also have a simpler implementation as they don't require to propagate arrival time bounds and no further oracle problem has to be solved. On top of that all timing paths are simultaneously represented. This avoids situations where a single failing path worsens unrelated nets with the same endpoint. Arrival time customers do not yield a stable result without iterating their oracle, in contrast path resources work with the natural implementation.

Depending on the problem width, the theoretic runtime when using path resources may be worse. However, even if the problem width is unbounded, a different polynomial analysis can be made for path resources [Häh15]. For some algorithms, explicit arrival times may be needed. While it is also possible with the path resources to propagate fractional arrival times, these values are already available when using arrival time customers. In fact, their update mechanism may yield more stable arrival times that could improve the performance of an algorithm which relies on them.

As a first implementation we recommend timing path resources, due to their ease of implementation and the upsides pointed out above. For a detailed analysis, both variants should be tried. In Chapter 7 we will compare both possibilities for BONNROUTEBUFFER.

# **3.4** Topology Generation

Consider the sub-problem of finding a solution for single nets that minimizes the weighted resource usage. The resource sharing algorithm requires that this subproblem can at least be approximated. In practice, it is possible to find Steiner trees which are only a few percent away from the optimum length.

For the moment we assume that edge costs  $c : E(G) \to \mathbb{R}_{\geq 0}$  for the global routing graph are known. Later, we will obtain these costs by applying the resource sharing algorithm. Together with the edge cost function, the global routing graph induces a metric space (V(G), dist). By approximating the corresponding Steiner Tree problem, we could route a single net in a way that approximately minimizes the weighted cost of the used edges. We will augment this problem, by also considering a rough estimate of the arising delays. More formally, we define the topology generation problem as follows.

Problem 3: Topology Generation Problem

- **Input:** A metric space (M, dist), a net N with pin positions  $p : N \to M$ , a source  $s \in N$ . Delay budgets rat  $: N \setminus \{s\} \to \mathbb{R}_{\geq 0}$ .

- **Task:** Compute a topology for N, i.e., an arborescence A rooted in s, such that T is the set of leaves. The root has exactly one successor in A and all inner vertices have outdegree exactly 2. A mapping  $p': N \to M$ , such that p'(q) = p(q) for  $q \in N$ , such that

$$\operatorname{delay}(s,q) \le \operatorname{rat}(q) \text{ for } q \in N \setminus \{s\}.$$

Here, let Y[s,q] be the unique s-q path in A for  $q \in N$ . Then, the delay is defined as

$$\operatorname{delay}(s,q) := C \sum_{(v,w) \in Y[s,q]} \operatorname{dist}(p'(v), p'(w)).$$

Here C > 0 is a technology-dependent delay constant. The objective, which we minimize, is

$$\sum_{(v,w)\in E(A)} \operatorname{dist}(p'(v), p'(w)).$$

We also call the pair (A, p') a *placed topology*. Held and Rotter [HR13] give a bicriteria approximation algorithm, which has the following guarantee.

**Theorem 3.5** (Held and Rotter [HR13]). Let (M, dist) be a metric space, N a net with pin positions  $p: N \to M$ , and  $s \in N$  a source. Let  $\text{rat}: N \setminus \{s\} \to \mathbb{R}_{\geq 0}$ be such that a solution achieving those delay budgets exists. Let  $A_0, p_0$  be an initial placed topology. For each  $\epsilon > 0$  we can compute a placed topology (A, p'), such that

$$\operatorname{delay}(s,q) \le (1+\epsilon)\operatorname{rat}(q) \text{ for } q \in N \setminus \{s\}.$$

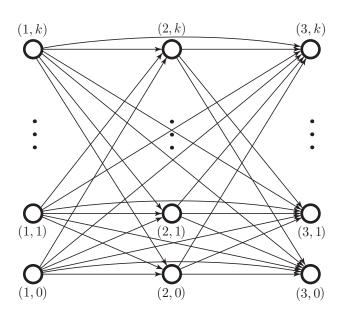

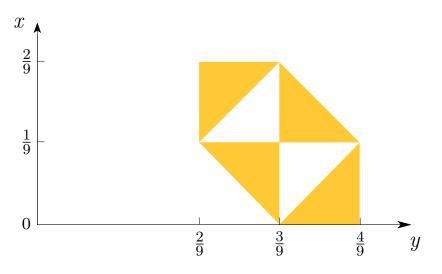

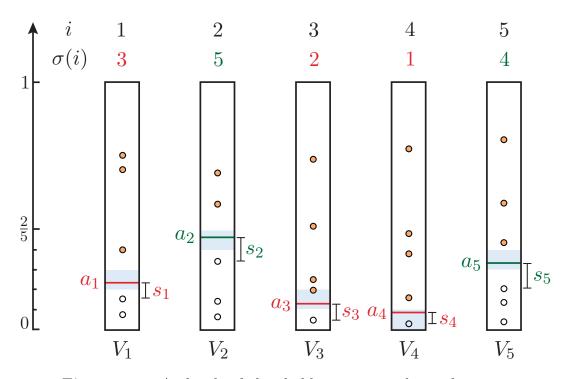

and