# Design and Development of Depleted Monolithic Active Pixel Sensors with Small Collection Electrode for High-Radiation Applications

Dissertation

zur

Erlangung des Doktorgrades (Dr. rer. nat.)

deı

Mathematisch-Naturwissenschaftlichen Fakultät

der

Rheinischen Friedrich-Wilhelms-Universität Bonn

von

Konstantinos Moustakas

aus

Larisa, Griechenland

Bonn, April 2021

| A 6 11 11 11 11 11 11 11 11 11 11 11 11 1          |                                                                                            |

|----------------------------------------------------|--------------------------------------------------------------------------------------------|

| Angefertigt mit Gener<br>Friedrich-Wilhelms-U      | nmigung der Mathematisch-Naturwissenschaftlichen Fakultät der Rheinischen Iniversität Bonn |

|                                                    |                                                                                            |

| <ol> <li>Gutachter:</li> <li>Gutachter:</li> </ol> | Prof. Dr. Norbert Wermes Prof. Dr. Klaus Desch                                             |

| Tag der Promotion:<br>Erscheinungsjahr:            | 09.09.2021<br>2021                                                                         |

|                                                    |                                                                                            |

|                                                    |                                                                                            |

## **Contents**

| 1 | Intro | duction   | n                                                              |                                                             | 1  |  |  |  |

|---|-------|-----------|----------------------------------------------------------------|-------------------------------------------------------------|----|--|--|--|

| 2 | Cha   | llenges   | ges and Requirements for the New Generation of Pixel Detectors |                                                             |    |  |  |  |

|   | 2.1   | Pixel c   | letectors fo                                                   | or particle tracking and vertex identification              | 5  |  |  |  |

|   |       | 2.1.1     | Position                                                       | resolution                                                  | 7  |  |  |  |

|   |       | 2.1.2     | Multiple                                                       | scattering                                                  | 7  |  |  |  |

|   |       | 2.1.3     | Impact p                                                       | arameter and vertex resolution                              | 8  |  |  |  |

|   |       | 2.1.4     | Momento                                                        | um resolution                                               | 9  |  |  |  |

|   | 2.2   | Challe    | nges and r                                                     | equirements for state-of-the-art and future trackers        | 10 |  |  |  |

|   |       | 2.2.1     | The high                                                       | luminosity LHC (HL-LHC)                                     | 13 |  |  |  |

|   |       | 2.2.2     | Pixel det                                                      | ectors for the HL-LHC: the ATLAS ITk upgrade                | 14 |  |  |  |

| 3 | Mon   | olithic l | Pixel Dete                                                     | ctor Fundamentals                                           | 19 |  |  |  |

| • | 3.1   |           |                                                                | fundamentals and the state-of-the-art: Hybrid pixels        | 19 |  |  |  |

|   |       | 3.1.1     |                                                                | or: signal generation and formation                         | 20 |  |  |  |

|   |       |           | 3.1.1.1                                                        | Energy loss of charged particles                            | 20 |  |  |  |

|   |       |           | 3.1.1.2                                                        | Charge generation                                           | 22 |  |  |  |

|   |       |           | 3.1.1.3                                                        | Charge transport                                            | 23 |  |  |  |

|   |       |           | 3.1.1.4                                                        | The p-n junction and sensor depletion                       | 24 |  |  |  |

|   |       |           | 3.1.1.5                                                        | Signal formation                                            | 27 |  |  |  |

|   |       |           | 3.1.1.6                                                        | Radiation effects - bulk damage                             | 27 |  |  |  |

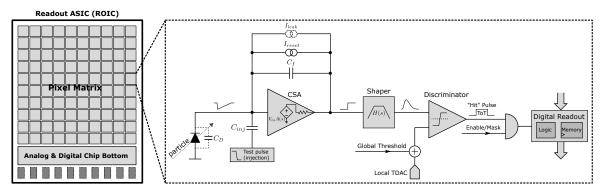

|   |       | 3.1.2     | The read                                                       | out ASIC: signal detection and processing                   | 29 |  |  |  |

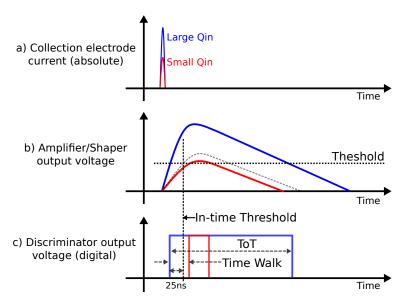

|   |       |           | 3.1.2.1                                                        | Performance criteria and design aspects                     | 31 |  |  |  |

|   |       |           | 3.1.2.2                                                        | Noise Sources                                               | 35 |  |  |  |

|   |       |           | 3.1.2.3                                                        | The charge sensitive pre-amplifier                          | 37 |  |  |  |

|   |       |           | 3.1.2.4                                                        | The importance of the Q/C ratio for high analog performance | 40 |  |  |  |

|   |       |           | 3.1.2.5                                                        | Readout architecture                                        | 41 |  |  |  |

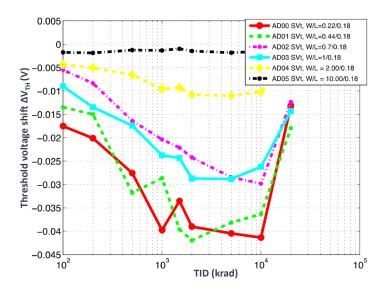

|   |       |           | 3.1.2.6                                                        | Radiation effects on the ROIC - surface damage              | 43 |  |  |  |

|   | 3.2   | The m     | onolithic a                                                    | approach: DMAPS                                             | 44 |  |  |  |

|   |       | 3.2.1     | Monolith                                                       | nic active pixel sensors (MAPS)                             | 45 |  |  |  |

|   |       | 3.2.2     |                                                                | monolithic active pixel sensors (DMAPS)                     | 45 |  |  |  |

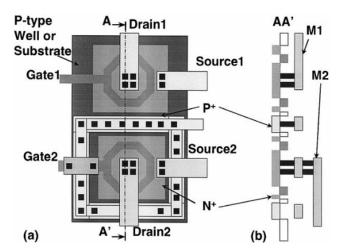

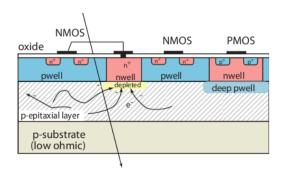

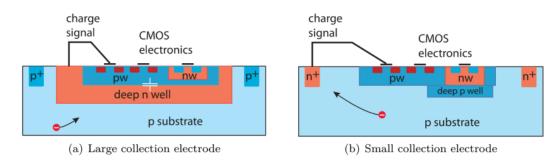

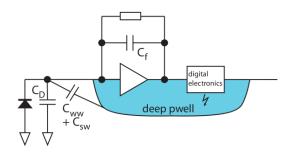

|   |       |           | 3.2.2.1                                                        | DMAPS implementation concepts                               | 47 |  |  |  |

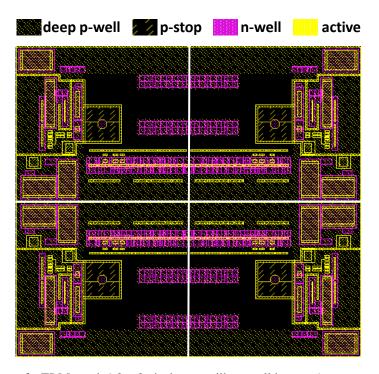

| 4 Development of the TJ-Monopix small collection electrode DMAPS in 180 nm CM 4.1 Small collection electrode DMAPS pixel concept in the TowerJazz 180 nm CM |        |          |                                                                    |          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|--------------------------------------------------------------------|----------|--|

| process                                                                                                                                                     |        |          |                                                                    |          |  |

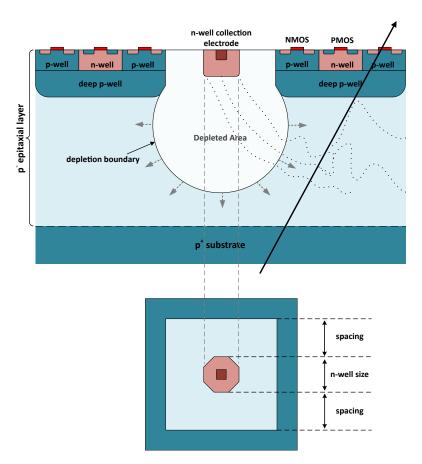

|                                                                                                                                                             |        | 4.1.1    | Monolithic pixels in the standard TowerJazz 180 nm CMOS process    | 52<br>52 |  |

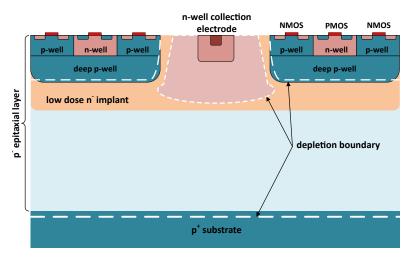

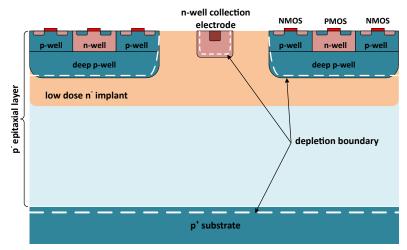

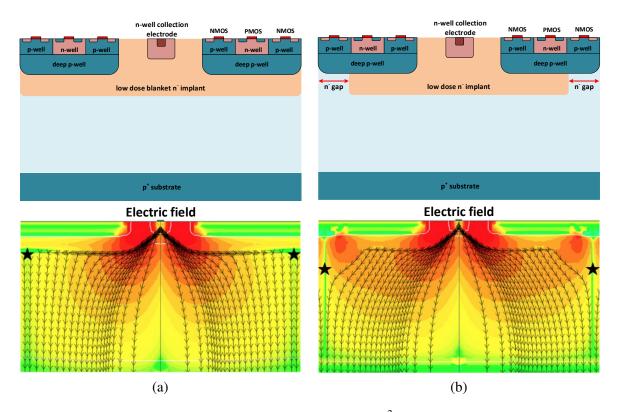

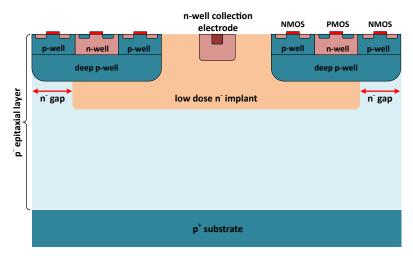

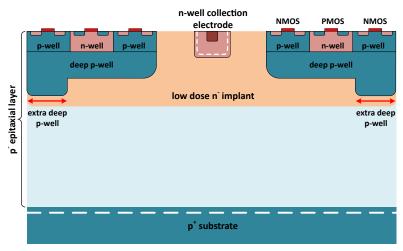

|                                                                                                                                                             |        | 4.1.2    | Process modification towards full depletion of the sensitive layer |          |  |

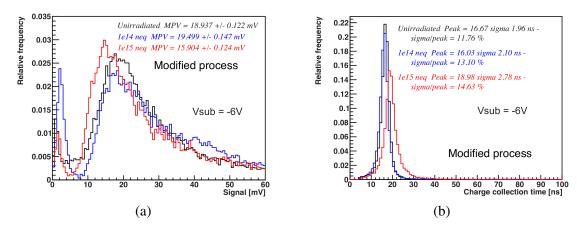

|                                                                                                                                                             |        | 7.1.2    | 4.1.2.1 Modified process sensor first tests                        |          |  |

|                                                                                                                                                             |        | 4.1.3    | Optimization for lateral field enhancement                         |          |  |

|                                                                                                                                                             |        | 4.1.4    | High resistivity thick Czochralski substrate alternative           |          |  |

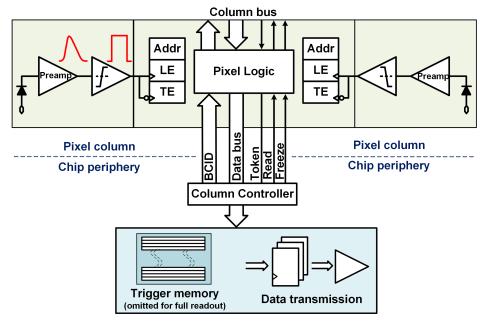

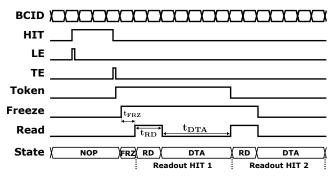

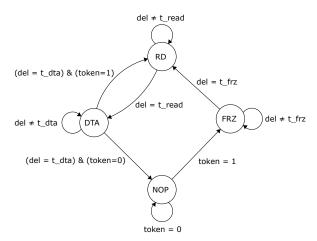

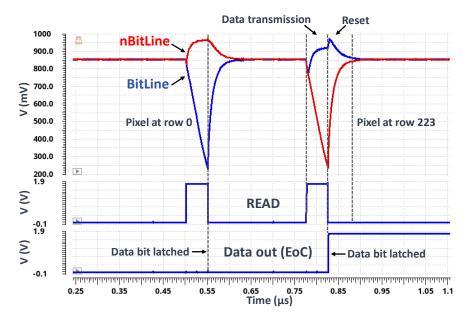

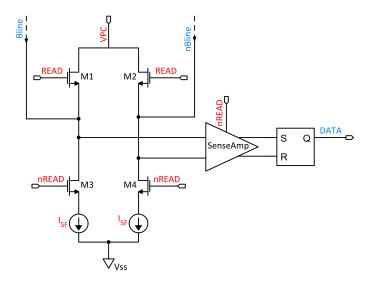

|                                                                                                                                                             | 4.2    |          | lumn-drain readout architecture                                    |          |  |

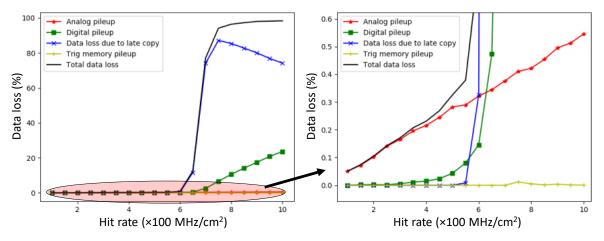

|                                                                                                                                                             | 4.2    | 4.2.1    | Hit rate capability simulation                                     |          |  |

|                                                                                                                                                             | 12     |          |                                                                    |          |  |

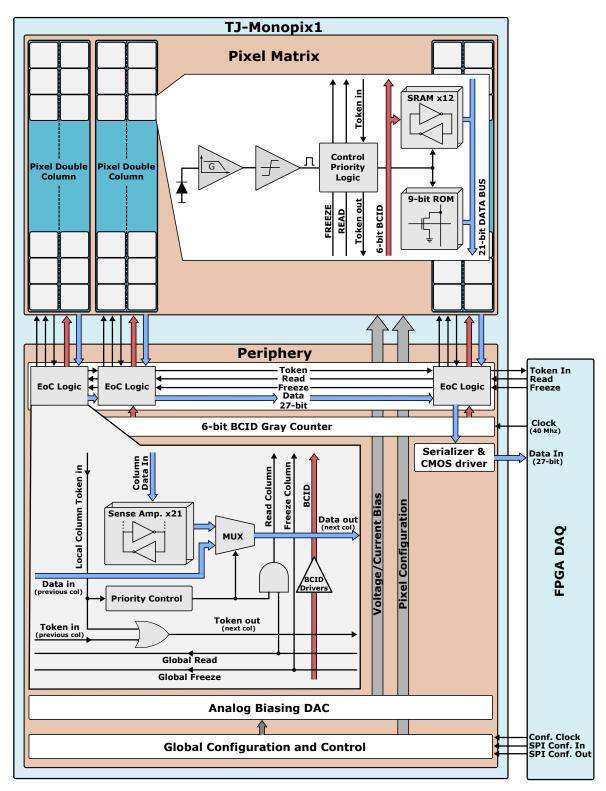

|                                                                                                                                                             | 4.3    | 4.3.1    | of the TJ-Monopix1 demonstrator chip                               |          |  |

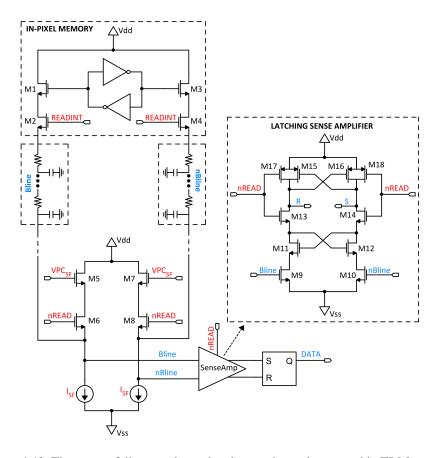

|                                                                                                                                                             |        | 4.3.1    | Pixel design and layout                                            |          |  |

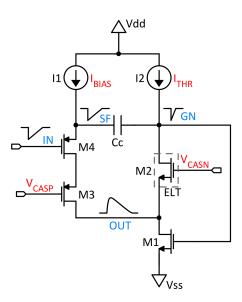

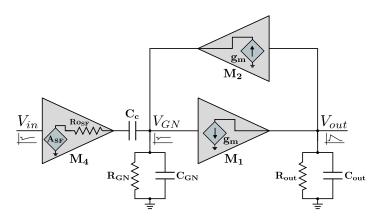

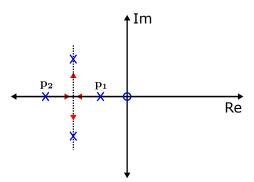

|                                                                                                                                                             |        |          | 4.3.1.1 Front-end design                                           |          |  |

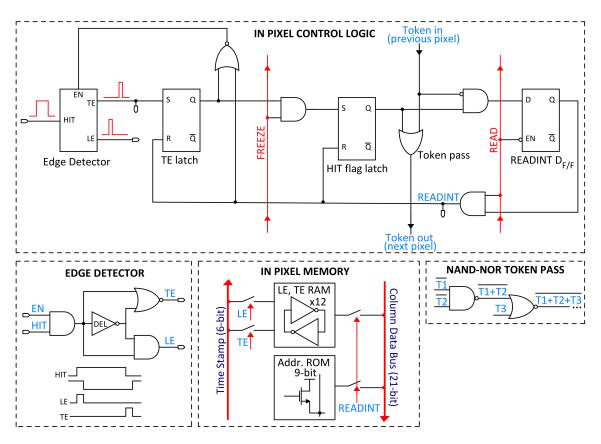

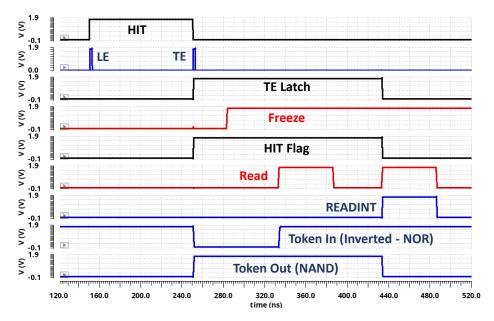

|                                                                                                                                                             |        |          | 4.3.1.2 In-pixel digital logic implementation                      |          |  |

|                                                                                                                                                             |        |          | 4.3.1.3 Test features                                              |          |  |

|                                                                                                                                                             |        | 4.3.2    | Chip design and architecture                                       |          |  |

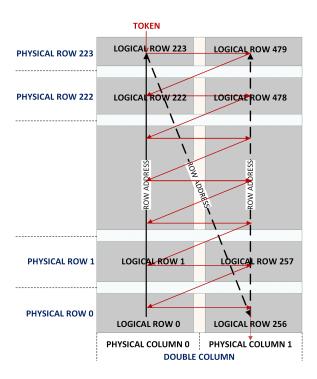

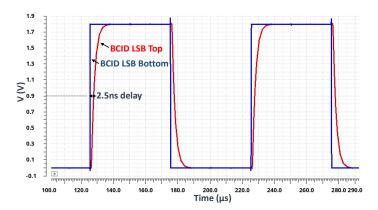

|                                                                                                                                                             |        |          | 4.3.2.1 BCID distribution and timing                               |          |  |

|                                                                                                                                                             |        |          | 4.3.2.2 Column-bus readout                                         |          |  |

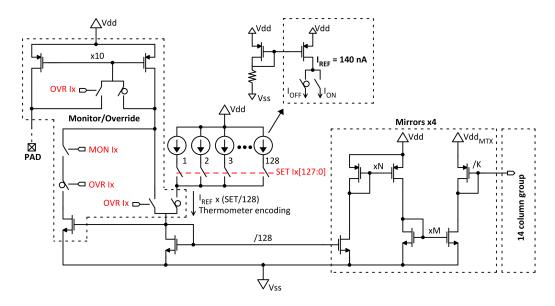

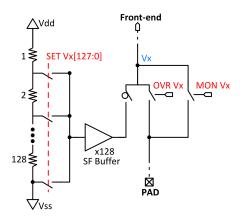

|                                                                                                                                                             |        |          | 4.3.2.3 Analog bias generation                                     |          |  |

|                                                                                                                                                             | 4.4    |          | nopix1 measurement and characterization                            |          |  |

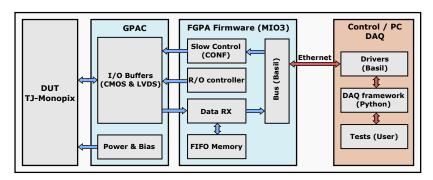

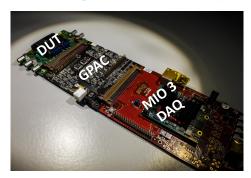

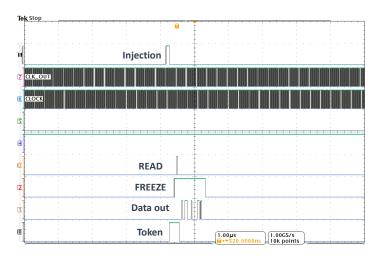

|                                                                                                                                                             |        | 4.4.1    | Readout system and test setup                                      |          |  |

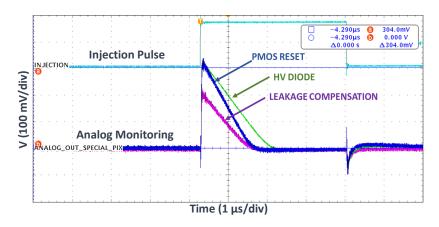

|                                                                                                                                                             |        | 4.4.2    | Single pixel measurements                                          | 21       |  |

|                                                                                                                                                             |        |          | 4.4.2.1 Analog front-end output                                    | 21       |  |

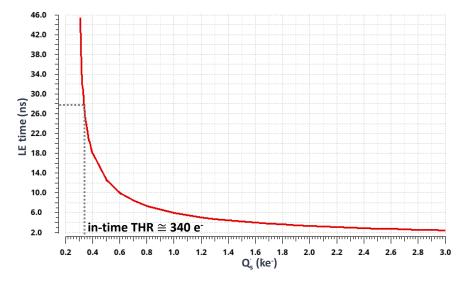

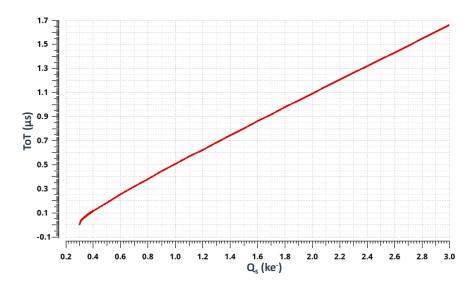

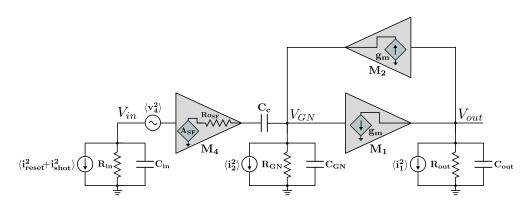

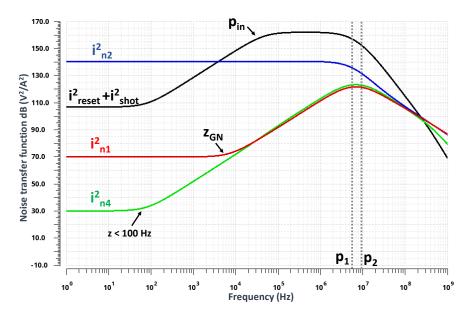

|                                                                                                                                                             |        |          | 4.4.2.2 Timing response and ToT                                    | 24       |  |

|                                                                                                                                                             |        |          | 4.4.2.3 Radioactive source measurements                            | 25       |  |

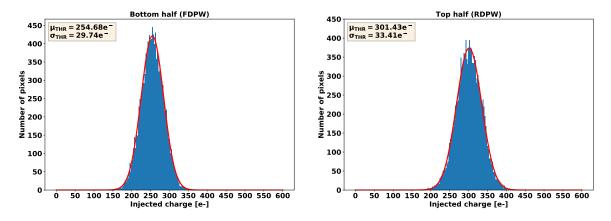

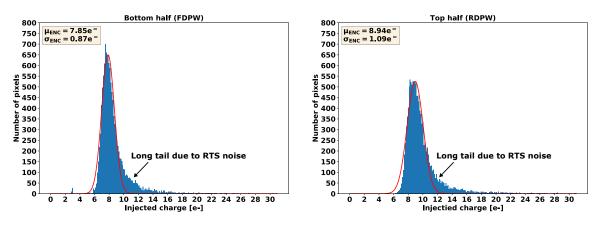

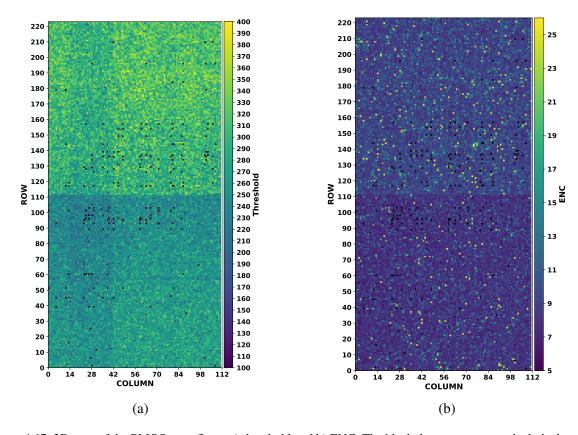

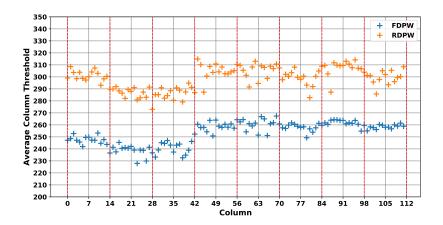

|                                                                                                                                                             |        | 4.4.3    | Injection scan characterization: Noise and threshold dispersion    | 27       |  |

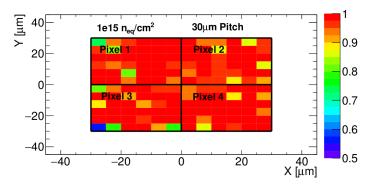

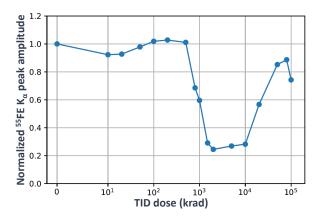

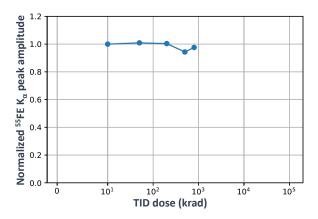

|                                                                                                                                                             |        | 4.4.4    | Performance after irradiation                                      | 33       |  |

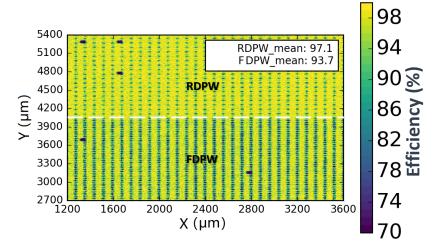

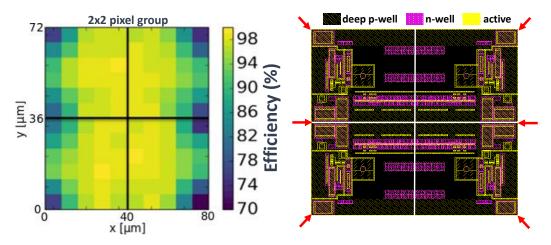

|                                                                                                                                                             |        | 4.4.5    | Detection efficiency measurement                                   | 35       |  |

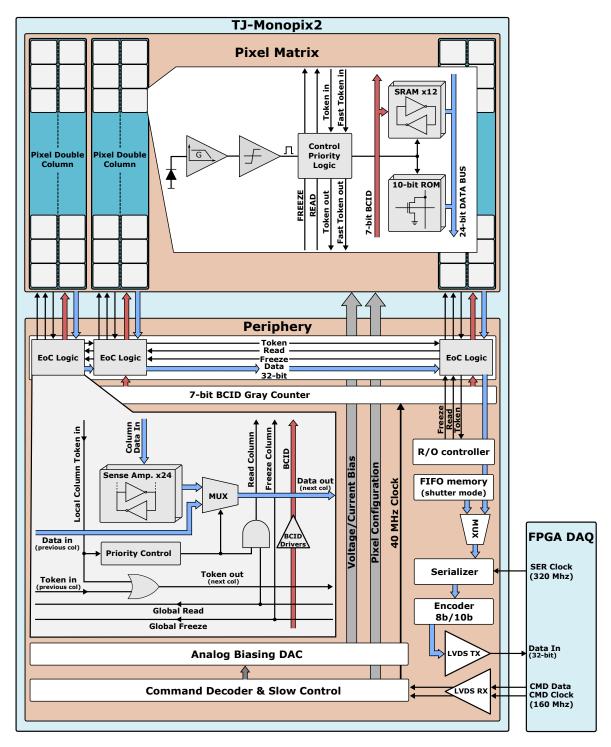

|                                                                                                                                                             | 4.5    | Design   | of the TJ-Monopix2 next generation full scale prototype            | 38       |  |

|                                                                                                                                                             |        | 4.5.1    | Pixel design and layout                                            | 40       |  |

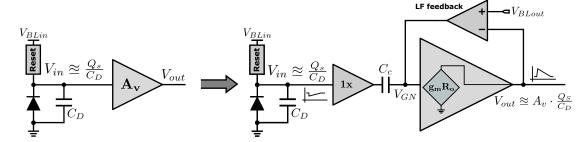

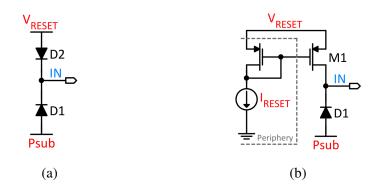

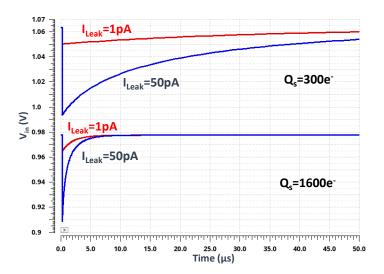

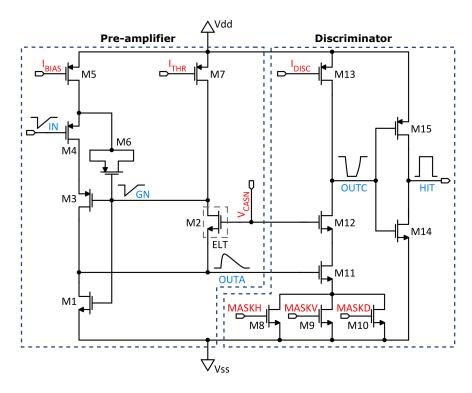

|                                                                                                                                                             |        |          | 4.5.1.1 Improved front-end circuit design                          | 42       |  |

|                                                                                                                                                             |        |          | 4.5.1.2 Threshold tuning and masking                               | 56       |  |

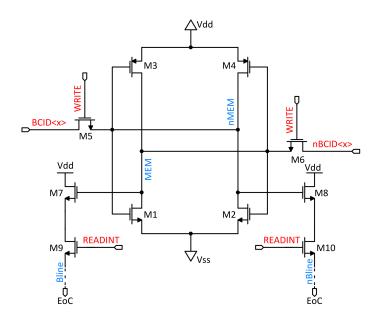

|                                                                                                                                                             |        |          | 4.5.1.3 In-pixel readout logic                                     |          |  |

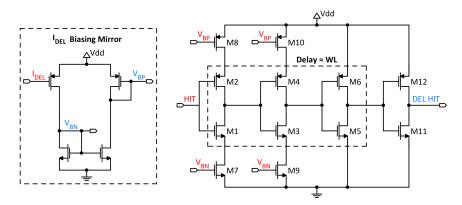

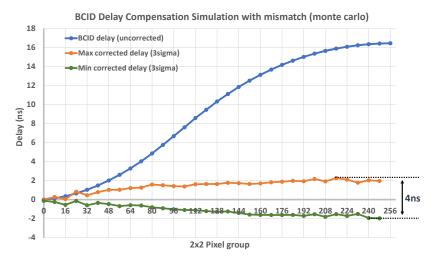

|                                                                                                                                                             |        |          | 4.5.1.4 BCID delay compensation                                    |          |  |

|                                                                                                                                                             |        |          | 4.5.1.5 Test features                                              |          |  |

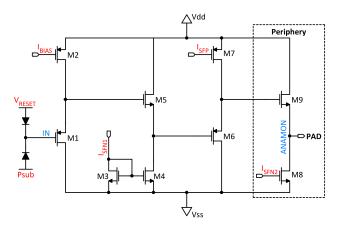

|                                                                                                                                                             |        | 4.5.2    | Chip design and architecture                                       |          |  |

|                                                                                                                                                             |        |          | 4.5.2.1 Current mode column-bus readout                            |          |  |

|                                                                                                                                                             |        |          | 4.5.2.2 Double column simulation                                   |          |  |

|                                                                                                                                                             |        |          | 4.5.2.3 Analog bias generation                                     |          |  |

|                                                                                                                                                             |        |          | 4.5.2.4 Data transmission                                          |          |  |

|                                                                                                                                                             |        |          |                                                                    |          |  |

| 5                                                                                                                                                           | Con    | clusions | s and outlook 1                                                    | 75       |  |

| Dil                                                                                                                                                         | alioar | anhy     | 4'                                                                 | 77       |  |

| List of Figures  | 185 |

|------------------|-----|

| List of Tables   | 193 |

| Acknowledgements | 195 |

## Introduction

Understanding the nature of reality can be considered the ultimate goal of human intellect. The idea that the universe is composed of fundamental blocks was first proposed by Democritus. It remained only conceptual until starting from the early  $20^{th}$  century a sequence of fascinating discoveries coupled with leaps in technological capabilities led to the establishment of the standard model of particle physics which describes the elementary particles and their interactions with great precision. Progress in nuclear and particle physics is driven by the development of detectors that provide information about the properties of particles and radiation interacting with them. Following the discovery of radioactivity by H.Becquerel in 1896, the invention of the cloud chamber [1] and subsequently the bubble chamber [2] opened new horizons by allowing the visualization of particles and their interactions through the observation of their tracks. Even though early detectors have led to the discovery of many new particles, photographic exposure was the only way of recording complex interactions up until the 1980s. Therefore, their main limitation was the inability to cope with high interaction rates and perform fast analysis of the results.

Modern experiments using particle colliders require the simultaneous detection of hundreds of particle tracks with micrometer spacial and nanosecond timing resolution. The first step towards fully electronic readout was the development of the multi-wire proportional chamber [3] which allowed the detection of particle tracks with accuracy in the order or 1 mm, but the leap in detector technology that provided the means to address such requirements stems from the invention of the transistor and the evolution of silicon microelectronics technology. Miniaturization of electronic devices has progressed exponentially over the decades following the prediction of Moore's law stating that the number of transistors in integrated circuits doubles every  $\approx$ 2 years, while manufacturing costs are reduced. Although semiconductor detectors have been used in the 1960s for gamma ray energy measurements, the key that revolutionized measurement quality is the ability to manufacture position-sensitive segmented detectors with micro-structured electrodes in the range of 50-100  $\mu$ m. Silicon microstrip detectors [4], in which one electrode is segmented in thin parallel strips, were developed in the 1980s and are still in use today as part of tracking detectors further away from the interaction point. They feature channel density of the order of 100 channels/cm² and spatial resolution in the order of 10  $\mu$ m.

Pixel detectors [5] are the next step in this evolution as they require more sophisticated technologies. While there is no large improvement in spatial resolution, their main advantage is that they return true 3D space points, which is a necessity for pattern recognition, tracking and reconstructing vertices

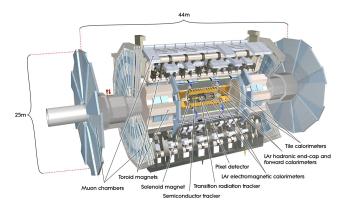

of short-lived particles. Furthermore they combine low material budget with channel densities higher than 5000 channels/cm $^2$ . Each pixel is an independent smart sensing element that incorporates advanced functionality to condition and process the signal and temporarily store data to be subsequently transmitted. This level of integration has been only achievable with modern sub  $\mu$ m Complementary Metal Oxide Semiconductor (CMOS) processes and renders pixel detectors capable of coping with high interaction rates and energies that are essential in probing of increasingly rare processes. Therefore, they are the instrument of choice for tracking and vertexing of particles close to the interaction point of three experiments at the Large Hadron Collider (LHC) [6] at the European Organization for Nuclear Research (CERN). Pixel detectors have been crucial in the experimental discovery of the Higgs boson [7, 8] by the ATLAS [9] (A Toroidal LHC Apparatus) and CMS [10] (Compact Muon Solenoid) detectors. The layout of the ATLAS detector is shown in Fig. 1.1(a), while an example candidate Higgs boson event as captured by the ATLAS detector is depicted in Fig. 1.1(b). No other detector instrument is capable of addressing as well the unprecedented track density, rate and fierce radiation environment originating from the current LHC figures of 14 TeV center of mass energy and instantaneous luminosity up to  $2 \cdot 10^{34}$  cm $^{-2}$  s $^{-1}$ .

(a) The ATLAS experiment at CERN. The pixel detector is located close to the interaction point [9]

(b) Event display of a  $H \rightarrow 4e$  candidate event captured by the ATLAS detector in 2012 [11]

Figure 1.1: The ATLAS detector at the LHC

Hybrid pixel detectors [5, 12] in which the pixellated sensor-diode and the readout (R/O) chip are separate entities, mated by employing bumping and flip-chipping technology, have been invented for the LHC and have matured over the years. They are so far the only viable concept to achieve the required radiation tolerance and hit rate capability. Their disadvantages are most notably material thickness, production complexity and cost. An alternative approach that mitigates these drawbacks are the so-called Monolithic Active Pixel Sensors (MAPS) [13–16] that integrate the sensor and the readout electronics on the same silicon crystal and can be manufactured using commercial CMOS technologies. Their use has so far been restricted in low radiation environments due to slow and incomplete charge collection mainly by diffusion. Recently, advancements and freedom in CMOS technologies allowing the use of high-voltage (HV) and high-resistivity (HR) add-ons and modifications have come in the R&D focus of monolithic pixels for high rate/radiation levels. New MAPS developments, called Depleted Monolithic Active Pixel Sensors (DMAPS) [17–21] are full CMOS pixel structures with fast charge collection by drift in a depleted active volume.

DMAPS development has been mainly driven by the High-Luminosity upgrade of the LHC (HL-LHC) [22, 23] in 2026. To be able to cope with an order of magnitude increase in luminosity, tracking detectors will be completely replaced and new generations of pixel detectors are being devised. Although hybrid pixels have been selected as the baseline for the CMS and ATLAS inner tracker (ITk) [24, 25] upgrade and materialized through the RD53 collaboration [26], CMOS DMAPS have been proposed as a cost and production efficient solution to cover the large area of the ATLAS ITk pixel detector outer layer, where the requirements in terms of occupancy and radiation are comparable to the current ATLAS pixel detector inner layers [9, 27]. Different prototyping designs in various technologies have been developed in the framework of an ATLAS CMOS demonstrator program [24]. After the successful characterization of stand-alone sensors, as well as pixel arrays bonded to a dedicated readout chip (usually FE-I4 [28]), the community engaged on the design of large fully monolithic CMOS pixel matrices with on-chip digital readout. Currently, there is high R&D swing on DMAPS, which is expected to grow as they are considered the preferred technology for future ultra-light, highly-granular, poly-layer vertex detectors. Furthermore, as was the case for hybrid pixels, imaging devices using MAPS are also spinning off targeting astrophysics, biomedical and crystallography applications using X-ray and synchrotron radiation.

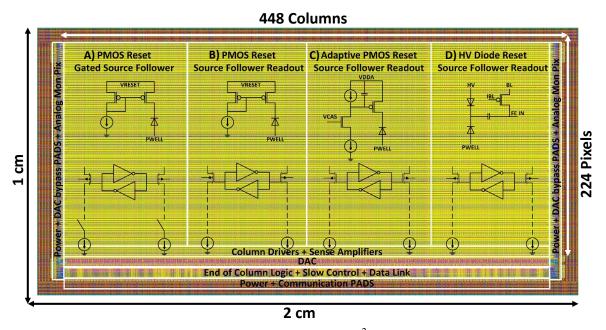

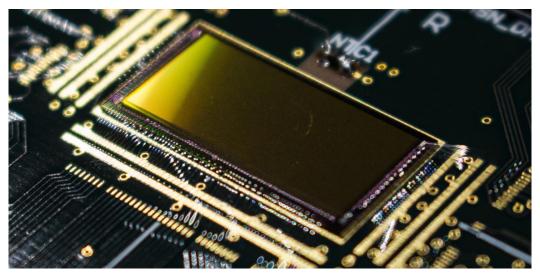

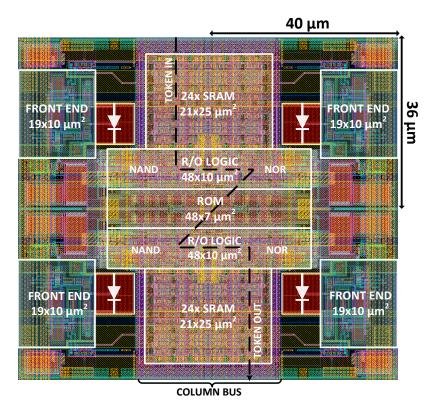

This thesis is dedicated to the design and development of large scale DMAPS prototypes with small collection electrode and fully integrated standalone readout architecture for high rate and high radiation applications such as the ATLAS ITk outer pixel layers. A small collection electrode leads to high granularity and low power consumption but its charge collection properties are not inherently suited for high radiation environments. In order to enhance radiation tolerance, a novel modification of the TowerJazz 180 nm CMOS imaging process [29] has been employed. The first, half scale  $(1 \times 2 \text{ cm}^2)$ , prototype chip that was developed on the modified process is called TJ-Monopix1 [30–32] and has been successfully characterized and proven to be fully functional [33, 34]. TJ-Monopix2 is a full scale  $(2 \times 2 \text{ cm}^2)$  successor that incorporates several improvements and addresses the shortcomings of TJ-Monopix1 towards a fully efficient DMAPS implementation with small collection electrode and is currently in the initial testing phase.

# Challenges and Requirements for the New Generation of Pixel Detectors

## 2.1 Pixel detectors for particle tracking and vertex identification

Pixel detectors are an essential part of experimental high-energy physics instrumentation. In this context, they constitute tracking detectors that image the trajectories of charged particles and are highly segmented and fast i.e. able to capture millions of events (images) per second. When specifically optimized to topologically reconstruct the displaced vertex structure of interactions, indicating particle creation or annihilation they are called vertex detectors.

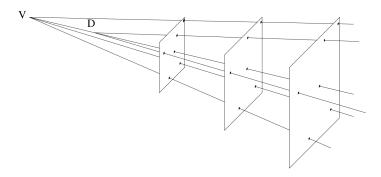

The development of high-granularity solid-state pixel detectors has been triggered mainly by the possibility of studying short-lived particles and the capability of coping with high interaction rates and energies (number of particles) in modern particle accelerators. High-energy colliders can generate elementary particle collisions at a high rate (>10 MHz), each producing 10-100 particles. Some rare, short-lived particles such as heavy quarks and leptons, that are of particular interest, quickly decay into a few secondary particles. The primary vertex indicates the location of the initial hard interaction, while secondary vertices often reflect the presence of a heavy particle such as a charm quark or a tau lepton. The topology of such a decay is depicted in Fig. 2.1.

Figure 2.1: Topology of a short-lived particle decay. V indicates the collision vertex while D indicates the decay vertex. Three pixel detector planes provide true three-dimensional (3D) space points are used for track reconstruction [5].

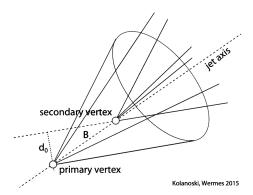

The tracker is therefore fundamental in the identification of jets (tagging) such as b-jets and  $\tau$ -leptons that signify important physics processes. The decay of B-hadrons and  $\tau$ -leptons is mediated by the weak interaction and usually takes place inside the beam pipe with a decay length that is increased by the Lorentz boost to  $l_{dec} = \beta \gamma c \tau_{dec}$  where  $\tau_{dec}$  is the particle life-time. An example of an event at a collider experiment which contains the decay of a B hadron is shown in Fig. 2.2. Extrapolated tracks that miss the primary interaction point suggest secondary decay vertices. This deviation is quantified by the impact parameter  $d_0$  which is defined as the closest approach to the interaction point at the momentum deflection plane. The resolution of the impact parameter  $\sigma_{d_0}$  is the primary figure of merit for vertex tracking accuracy and as will be shown depends on the detector single point resolution, geometry and material budget. With a single point (position) resolution of  $\approx 10 \, \mu m$ , a vertex separation in the order of  $100 \, \mu m$  can be typically resolved [35].

Figure 2.2: Sketch of a *b*-quark jet. A *B* hadron decays at a secondary vertex, which is quantified by the distance of the closest approach from the primary vertex, called the impact parameter  $d_0$  [35].

In modern high-energy collider experiments, while seeking new physics, increasingly rare processes must be probed. Therefore, a high interaction rate is essential. Combined with the high primary particle energy, it results in a large amount of particles and dense tracks being generated. Thus, the tracker does not only need to be accurate but must also be highly granular meaning that enough sensing elements are available to reduce pile-up and distinguish tracks that pass close to the decay point, a feature unique to pixel detectors.

Particle detectors at accelerators are usually immersed in a magnetic field and act as a magnetic spectrometer that allows the determination of the momentum of charged particles. Therefore, another role of tracking detectors is the precise reconstruction of the particle track curvature that infers momentum and charge. In collider experiments, typically an arrangement of a solenoid spectrometer is used where the beams cross the center of the solenoid. To cover as high percentage as possible of the full solid angle, but also be mechanically feasible, the sensitive layers are usually arranged as coaxial barrel layers supplemented by several end-cap disks.

A number of competing conditions such as the physics needs, the interaction rate and intensity, technical capabilities and the available funds influence the design of a pixel detector and the solution to this optimization problem has led to a variety of designs in use today and envisioned in the future. In this chapter, the basic design parameters that influence the tracking performance of pixel detectors will be presented. State-of-the art, performance drivers and the requirements for the new generation of pixel sensors will be also discussed with emphasis on the HL-LHC ATLAS inner tracker (ITk)

upgrade as it forms the basis for the specifications of the pixel sensors developed and presented in this work.

#### 2.1.1 Position resolution

Pixel detectors employ structured electrodes to take a precise measurement of the space coordinates of a signal in a reference plane. The resolution is determined by the segmentation width (pixel pitch), the signal distribution function to neighboring pixels (charge sharing) and the signal to noise ratio (SNR), therefore the minimum achievable threshold. In some applications only binary information is given while in others the signal is measured in proportion to the integrated charge (analog readout). In order to understand the basic principles of vertex measurement, a simple approximation of a noiseless binary readout assuming uniform particle occupancy and full efficiency is sufficient. To simplify the analysis, the spatial resolution across one dimension (x coordinate) will be considered. The extension towards two orthogonal coordinates is straightforward. For equal pitch and resolution across the x and y dimensions, the two dimensional space resolution is  $\sigma_r = \sigma_x \cdot \sqrt{2}$  [35].

A binary response is given for example when the charge density distribution width is small compared to the electrode width and no interpolation is done. The spatial resolution is defined by the standard deviation of the distribution of the measurement error, that is calculated by the root mean square function. For the presumed uniform distribution f(x) = 1 of particle illumination across the electrode width d from -d/2 to d/2 the standard deviation of the measurement error is given by:

$$\sigma_x^2 = \frac{\int_{-d/2}^{d/2} x^2 f(x) \, dx}{\int_{-d/2}^{d/2} f(x) \, dx} \Rightarrow \sigma_x = \frac{d}{\sqrt{12}}$$

(2.1)

The position resolution can be improved with the expense of a larger total data volume by recording and transmitting analog hit charge information per pixel. In this case the reconstructed hit position can be obtained by the center of gravity method:

$$x_{\text{rec}} = \frac{\sum (S_i + n_i) x_i}{\sum (S_i + n_i)}$$

(2.2)

where the  $S_i$  and  $n_i$  are the signal and noise fractional weights respectively and  $x_i$  is the center of each individual pixel in the cluster [20, 35]. The optimal achievable resolution depends on the proper matching of the electrode width with the signal charge distribution for a given SNR. While silicon trackers have typically had granularities greater than or equal to the charge cloud deposit, in current detector development increased spatial and temporal granularity is essential to make use of the structure of charge deposits.

## 2.1.2 Multiple scattering

Charged particles passing though matter are scattered in the Coulomb field of the nuclei. This process is described by the Rutherford cross section which yields high probability for small angles. Therefore, for a not too thin scattering medium, a large number of independent scatters occur that can result in a significant deviation of the particle direction. This process is called multiple or Molière scattering and can be in most practical cases approximated by a Gaussian distribution. The characteristic quantity of

multiple scattering is the standard deviation of the distribution of the projected scattering angle which can be approximated by [35]:

$$\theta_{\rm ms} = \frac{0.0136 \,\text{GeV/c}}{p\beta} |z| \sqrt{\frac{x}{X_0}} \tag{2.3}$$

where p,  $\beta$  and z are momentum, normalized velocity and charge of the particle respectively and  $x/X_0$  is the path length in the scattering medium in units of the radiation length  $X_0$ . From (2.3) it is obvious that the uncertainty due to multiple scattering depends on p and becomes important for low momentum particles.

## 2.1.3 Impact parameter and vertex resolution

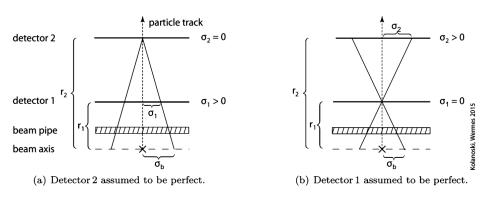

It is important to assess which parameters are crucial for a microvertex detector with regards to its accuracy especially in terms of pixel pitch, detector geometry and area (number of layers, level arm, distance of the first layer to the primary vertex) and material thickness. Doing so will allow us to understand the significance of high granularity, low mass and low production effort that monolithic pixels (DMAPS) can offer. We can start the analysis by considering a simple, but indicative, case of a two layer vertex detector installed outside of the beam pipe near the interaction point as shown in Fig. 2.3. For simplicity, we assume planar modules and straight tracks traversing the layers perpendicularly.

Figure 2.3: Simplified two-layer vertex detector. The layers are cylindrically arranged at distances  $r_1, r_2$  and have position resolutions  $\sigma_1, \sigma_2$  in the plane perpendicular to the beam [35].

The impact parameter error of the track,  $\sigma_b$  can be calculated by assuming that in each case one of the two layers is perfectly accurate. It can be geometrically determined by the resolution of each layer and the aspect ratio of the two layers and is equal to [12, 35]:

$$\sigma_b^2 = \left(\frac{r_1}{r_2 - r_1}\sigma_1\right)^2 + \left(\frac{r_2}{r_2 - r_1}\sigma_2\right)^2 \tag{2.4}$$

This result can be expanded for a linear track fit in a general case of N equally distributed layers with spacing  $L_p/(N-1)$  measured with spatial resolution  $\sigma_{\text{meas}}$ , as given by [35]:

$$\sigma_{d_0} = \frac{\sigma_{\text{meas}}}{\sqrt{N}} \sqrt{1 + \frac{12(N-1)}{N+1} \left(\frac{x_0}{L_n}\right)^2}$$

(2.5)

where  $x_0/L_p$  is the ratio of the extrapolation lever arm to the length over which the measurement points are distributed. If the origin of the reference frame is chosen in the center of the track,  $x_0$  is the distance from the center of measurements to the extrapolation point (primary vertex).

The impact parameter resolution is further reduced by the effects of multiple scattering discussed in section 2.1.2. For the aforementioned case of equally spaced detector layers, equal thickness d and single layer scattering angles  $\theta_{\text{ms,sl}}$ , an estimator of the slope error  $\sigma_b$  can be calculated by summing in quadrature the contribution of each layer [35]:

$$\sigma_{b,\text{ms}} = \frac{0.0136 \,\text{GeV/c}}{p\beta \sin \theta} |z| \sqrt{\frac{d/\sin \theta}{X_0}} \sqrt{\frac{N(2N-1)}{6(N-1)}}$$

(2.6)

where d is the thickness of the detector plane and  $\theta$  is the angle between the trajectory and the direction of the magnetic field. Considering only the error due to multiple scattering, the primary vertex can be extrapolated from the first layer at  $r_1$ . Therefore, the impact parameter error due to multiple scattering is given by:

$$\sigma_{d_0,\text{ms}} = \sigma_{b,\text{ms}} r_1 \tag{2.7}$$

with  $r_1$  being the distance from the first layer to the primary vertex.

To achieve high vertex resolution, high intrinsic position resolution (segmentation) and a large lever arm  $(L_p)$  is required. The innermost layer of the vertex detector should be as close as possible to the interaction point to take advantage of the short extrapolation length and its resolution is the most important. In general the minimal distance is limited by the beam pipe, the radius of which should not be too small because of the radiation background near the beam. Low detector material  $(x/X_0)$  is needed in order to minimize multiple scattering, especially for low momentum tracks.

#### 2.1.4 Momentum resolution

The transverse momentum  $p_T$  is calculated by the curvature  $\kappa$  of the particle track inside a magnetic field B:

$$p_T = \frac{0.3|z|B}{|\kappa|}, \quad [p_T] = \text{GeV}/c$$

(2.8)

It is typically determined by the measurement of the sagitta of the curved path between the points of the entrance into and exit from the detector volume. For a detector with N equally spaced layers and in the limit of large N, the resolution of the transverse momentum is given by the 'Gluckstern' formula, which is valid for high momenta where multiple scattering can be neglected [20, 35]:

$$\left(\frac{\sigma_{p_T}}{p_T}\right) = \frac{p_T}{0.3|z|} \frac{\sigma_{\text{meas}}}{L_p^2 B} \sqrt{\frac{720}{N+4}} \tag{2.9}$$

where  $\sigma_{\text{meas}}$  is the position resolution of each layer and  $L_p$  is the radial length of the detector. The contribution of multiple scattering to momentum resolution can be written as [20, 35]:

$$\left(\frac{\sigma_{p_T}}{p_T}\right)_{\text{ms}} = \frac{0.0136}{0.3\beta L_p B} \sqrt{\frac{(N-1) d/\sin\theta}{X_0}} \sqrt{C_N}$$

(2.10)

where  $L_p$  is the detector (tracker) length projected onto the plane perpendicular to the magnetic field

and  $(d/\sin\theta)/X_0$  is the total material thickness traversed by a particle incident with polar angle  $\theta$  with respect to the beam in units of radiation length.  $C_N$  is a factor that describes different detector layouts and depends on the number of layers. For the minimum of three layers (N=3) one obtains  $C_N=2.5$ , while for  $N\to\infty$  the continuous scattering case is approached with  $C_N\to1.33$ .

The dependence of momentum resolution to the lever arm  $L_p$  is strong and scales with  $L_p^2$ . To achieve a large lever arm while optimizing performance and cost, in most cases the tracker is split in layers with different technologies. High granularity pixel detectors are used for the innermost layers (vertex detector) while the outer layers of the tracker consist of less expensive concepts such as strip detectors. The error of momentum resolution due to position measurement increases with the transverse momentum  $P_T$  while the error due to multiple scattering is independent of  $P_T$ . Therefore, for small momenta the total error reaches a plateau given by the multiple scattering term while for high momenta the measurement term dominates.

## 2.2 Challenges and requirements for state-of-the-art and future trackers

Experiments at the energy frontier are dominated by large accelerators and multipurpose collider detectors. The current state-of-the-art is represented by the detectors in operation or under construction at the LHC at CERN, prominently by the ATLAS and CMS experiments. The challenges that drive ongoing development of detectors for hardon colliders can be broadly categorized into scale, intensity and performance [20]. Planned upgrades such as the High-Luminosity LHC (HL-LHC) [23] and the subsequent High-Energy LHC (HE-LHC) [36] and future hadron colliders such as the conceived Future Circular Collider (FCC) [37] focus on two main parameters that allow to refine the standard model and improve the physics reach: increasing the energy and intensity of the beam. By doing so, the number of interactions per bunch crossing drastically increases. From the pixel detector perspective two main demands arise: the ability store and process hits at a high rate per unit area and high radiation tolerance to survive the harsh environment close to the interaction point.

In order to cope with high hit rates, the pixel size has to be small and the outer radius of the detector has to be increased. Since every "hit" on the pixel detector must be time-stamped and stored for the trigger latency interval, more memory per unit area is required to be included in the readout integrated circuit (ROIC). Therefore, silicon CMOS technologies in smaller process nodes are needed to be exploited in order to achieve the required logic density. Higher intensity also means that in order to distinguish events of interest from the background, the trigger rate must be increased. Therefore, pixel detectors output much more data that requires integrated, fast electrical links that can maintain high signal quality while using low mass cables.

Challenges for lepton colliders such as the Belle II [38] experiment at superKEKB, the planned compact linear collider (CLIC) [39] at CERN and planned the international linear collider (ILC) [40] differ from those of hadron colliders. Exploring the physics potential requires precision measurements, especially at low momenta and mandates for higher granularity and lower mass by one to two orders of magnitude compared to the current LHC detectors. On the other hand, the requirements imposed by the beam structure, data rate and radiation dose are much more modest compared to the LHC. An exception is the time structure of the beam at CLIC that requires fast timing response due to the small bunch separation (0.5 ns).

The aforementioned challenges should be compounded by the basic performance of the sensor and readout electronics. The most important factors are the signal amplitude, the sensor capacitance and

leakage, the device specific transconductance and the noise of the ROIC. A set of these parameters and a maximum power budget defines an upper limit in the analog performance that is well understood and the ROIC should be designed to perform close to this limit.

Future trackers must function in extreme environments while maintaining or improving their performance. As previously discussed, high resolution demands a high-granularity, low-mass, polylayer detector close to the interaction point. Furthermore this should be achieved with low power consumption and low cost and production effort. The performance drivers and design aspects that emerge in detector R&D can be summarized as follows:

• Pixel size, hit rate and position resolution: The two main drivers for the sensor pixel pitch P are the position (single point) resolution and two track separation, both scaling as P and local occupancy scaling as the pixel area (P² for square pixels) times the readout time. In high rate environments, such as the HL-LHC, a small pixel size is necessary to maintain full efficiency and avoid pileup and becomes more important when the first layer is placed close to the interaction point in order to improve the resolution. Furthermore, smaller pixels help to keep the leakage current per pixel small and improve noise after irradiation. In order to further improve the resolution and two track separation, the analog charge information can be utilized given that the SNR is high enough. Recent developments [20] address the processing of multi-hit pixel clusters as complex objects to exploit directional information. A high channel count, especially in the case of analog readout, requires higher logic density and an efficient, fast, zero-suppressed readout.

When aiming for high resolution, the following limitations should be considered regarding the pixel size:

- The smallest pixel size is determined by the amount of in-pixel electronics that are necessary to amplify, discriminate and store the hit information.

- The spread of the charge cloud due to diffusion, which is given by:

$$\sigma_x = \sqrt{2D_x/u_D} \tag{2.11}$$

where D is the diffusion constant, x the drift distance to the electrode and  $u_D$  the drift velocity. The spread due to diffusion sets a constraint for the minimum pixel size since a pixel pitch below  $\sigma_x$  would lead to excessive charge sharing.

- The technological limits of detector fabrication and assembly. An example is the fine pitch bump bonding process in the case hybrid pixel detectors (see section 3.1).

- Material budget, radiation length and collection thickness: Multiple scattering dominates the resolution for precision track fitting, particularly at low momenta. It becomes extremely important for heavy-ion, nuclear physics and rare muon decay experiments that operate in a multiple scattering dominated regime. Therefore, the material inside the detector has to be as low as possible. Traditionally, the pixel sensor and ROIC were the most significant contributors to the total material budget. In current developments, thinner sensors are being explored in order to reduce the material, provide faster charge collection and improve the charge spread due to diffusion. Monolithic pixels (DMAPS) allow for very low material by combining the sensor and ROIC in the same silicon crystal. Thicknesses down to 50 µm can be achieved beyond which mechanical supports, wiring and cooling services typically dominate.

- Detector area, cost and power: Cost and power are two important constraints that scale with the detector total area. A large detector area is a consequence of the following requirements:

- Greater length along the beam direction that improves acceptance.

- A large number of measurements (N) improves the impact parameter accuracy due to the resulting higher position resolution  $\sigma_{\rm meas}$ . However, the resolution error due to multiple scattering also increases with N. Since having many measurement points is beneficial for pattern recognition and specific ionization measurements. in practice the number of layers must be optimized according the requirements and specific parameters of the detector.

- Large radii that reduce the local pixel occupancy, at least for the outer layers, and increase the lever arm  $L_p$  which improves track fitting and vertex resolution.

These requirements drive a strong focus on cost reduction which is also vital for valorization of the technologies developed for particle physics in other applications e.g. in the medical field. Since large areas have to be covered (> 10 m²), large volume manufacturing with less effort is essential. In the case of hybrid pixels, sensor manufacturing in commercial CMOS processes (passive sensors) is currently considered to reduce cost. DMAPS are not only manufactured in commercial processes, but also do not require the laborious bump-bonding process and therefore further reduce the cost and complexity (more details in section 3.2).

A large detector area and small pixel size result in millions of pixels that have to operate with tolerable power consumption. For a given ROIC CMOS process and power budget the analog performance and power consumption are essentially determined by the detector capacitance, which is therefore important to be minimized by optimizing the sensor technology. Furthermore, given the huge number of channels, powering the detector using a conventional parallel wire scheme becomes impractical. In the case of the HL-LHC, a serial powering scheme with on-chip regulators will be implemented in order to reduce the required wiring. Low power is mandatory for compact arrays that require very low multiple scattering if cooling does not dominate the overall material budget.

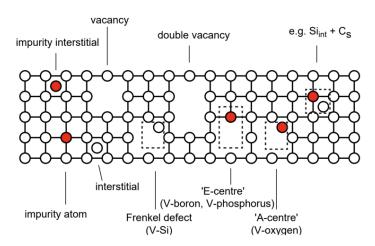

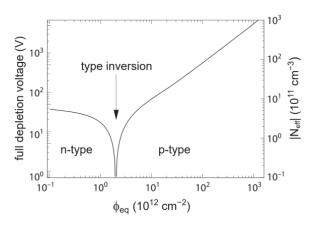

- Radiation tolerance: Radiation effects mainly the include the sensor bulk damage due to non Ionizing Energy Loss (NIEL) and the damage on the readout electronics due to the accumulated total Ionizing Dose (TID). The innermost layer of the vertex detector, which should be close to the beam pipe to improve resolution, is the most severely affected by radiation damage. Radiation tolerance has been an crucial performance aspect even for the current state-of-the art detectors at the LHC and has been extensively studied with the help of a strong R&D program led through the RD50 [41] collaboration. For high energy and high intensity future accelerators, radiation damage is expected to increase by more that an order of magnitude and will become one of the most critical challenges.

- *Time resolution:* The charge collection time is typically in the order of 3 10 ns and depends on the sensor thickness and electric field. It usually goes hand-in-hand with radiation tolerance as the later often relies on a fast signal collection by a strong drift field. For applications with particle bunches colliding at a specific frequency such as the LHC, the pixel detector has to be at least fast enough to assign a correct time stamp to each event. Very high timing resolution (< 100 ps), required to identify the common origin of particles, has not yet been achieved by pixel detectors and therefore different detector types such as scintillators are used to provide

this information. Recently, amplification structures in silicon such as the Low Gain Avalanche Diode (LGAD) [20] have been brought forward in an attempt to cope with these demands.

## 2.2.1 The high luminosity LHC (HL-LHC)

The Large Hadron Collider (LHC) [6] at the European Organization for Nuclear Research (CERN) is currently the most advanced particle accelerator. While it is mainly a proton collider, it can also operate with heavy ions. Protons in two counter-rotating beams are accelerated through a complex of accelerators, finally reaching a center of mass energy of 13 TeV in the 27 km long ring. The beams collide at four crossing points where the four largest experiments are located called ATLAS (A Toroidal LHC Apparatus) [9], CMS (Compact Muon Solenoid) [10], ALICE (A Large Ion Collider Experiment) [42] and LHCb [43]. The interactions between the counter-rotating beams are not continuous since the protons are bunched together and collide at discrete intervals, 25 ns apart, yielding a bunch crossing frequency of 40 MHz. The quantity that measures the ability of a particle accelerator to produce the required number of interactions is called luminosity  $\mathcal{L}$  and is defined as the ratio of the number of events per second dR/dt to the production cross-section  $\sigma_n$ :

$$\frac{\mathrm{d}R}{\mathrm{d}t} = \sigma_p \cdot \mathcal{L} \tag{2.12}$$

The luminosity can be semi-qualitatively obtained from:

$$\mathcal{L} = \frac{N^2}{t \cdot \sigma_{\text{eff}}} \tag{2.13}$$

where N is the number of protons in each beam (assuming they are equal), t is the time between bunches and  $\sigma_{\rm eff}$  is the effective cross section of the collision that depends on the beam profile. The two largest experiments, ATLAS and CMS, are currently designed to operate at a nominal luminosity equal to  $1 \cdot 10^{34} \, {\rm cm}^{-2} \, {\rm s}^{-1}$ , however a peak luminosity up to approximately  $2 \cdot 10^{34} \, {\rm cm}^{-2} \, {\rm s}^{-1}$  has been achieved before the Long Shutdown 2 (LS2) in 2019, while the integrated luminosity approached  $190 \, {\rm fb}^{-1}$ .

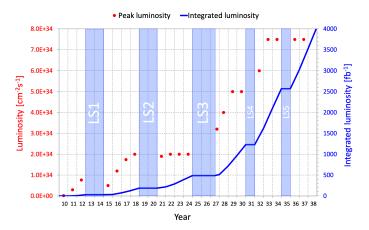

The LHC has been successful in the detection of the Higgs boson and has provided valuable precision measurements to refine the standard model. However, since rare processes are vital to increase the physics reach, the statistical gain of operating the accelerator beyond 2020 without significantly increasing the luminosity will become marginal. To improve statistics of potential interesting interactions and utilize the full potential of the LHC, a major upgrade is planned to take place during the long shutdown 3 (LS3). The timeline of the upgrade is shown in Fig. 2.4(a) and the expected luminosity is depicted in Fig. 2.4(b). After the HL-LHC installation is complete, the instantaneous luminosity will gradually increase to its nominal value of  $5 \cdot 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>, which is five times higher than the current LHC configuration, and can reach a maximum of  $7.5 \cdot 10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. The HL-LHC integrated luminosity is expected to become approximately 10 times higher than the integrated luminosity accumulated in the current LHC lifetime. Such an increase in intensity sets stringent requirements for the detector systems in terms of hit rate and radiation tolerance, especially in the case of the pixel detector inner layers. To cope with these requirements, the inner trackers of the CMS and ATLAS experiments will be upgraded.

(a) LHC baseline plan for the next decade and beyond. Runs in the HL-LHC configuration will begin after the LS3 [22].

(b) Forecast for peak luminosity (red dots) and integrated luminosity (blue line) in the HL-LHC era according to the ultimate HL-LHC parameters [23].

Figure 2.4: The HL-LHC upgrade schedule and luminosity forecast

## 2.2.2 Pixel detectors for the HL-LHC: the ATLAS ITk upgrade

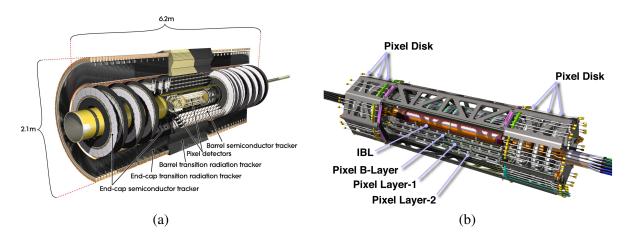

The current ATLAS Inner Detector (ID) [44] is depicted in Fig. 2.5 (a). It consists of the pixel detector, the semiconductor tracker (SCT) that is composed of silicon strips and the transition radiation tracker (TRT). The pixel detector, shown in Fig. 2.5 (b) was originally designed as a system with three barrel layers around the beam axis and three disks in each direction along it. It covers a total area of approximately 1.7 m<sup>2</sup> and is composed of 80 million silicon hybrid pixels of  $50 \times 400 \,\mu\text{m}^2$  size. During the long shutdown 2 (LS2), it was upgraded to improve the vertex resolution and efficiency in the pretense of high pile up. A fourth pixel layer, called the Insertable B-Layer (IBL) [27] was installed at r = 3.3 cm between the old innermost pixel layer and a new smaller radii beam pipe. Due to the higher track density during Run-2, the IBL operates with smaller pixels of  $50 \times 250 \,\mu\text{m}^2$  size in order to reduce occupancy.

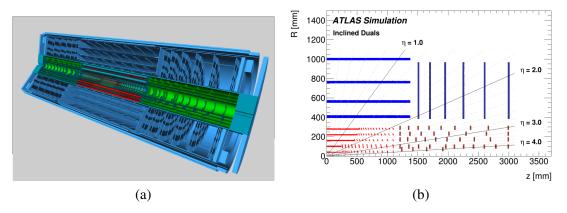

The LHC ATLAS inner detector will be replaced by the new ATLAS inner tracker (ITk) [24] for the HL-LHC operation. The proposed layout of the ATLAS ITk is shown in Fig. 2.6 (a). The total size is about the same as the ATLAS ID since the systems that surround it (e.g. calorimeter) will not be

Figure 2.5: a) Cut-out view of the ATLAS inner detector [44], b) Layout of the ATLAS pixel detector after LS1 [27].

Figure 2.6: a) Display of the ATLAS Phase-II Inner Tracker ITk with the inclined duals detector layout, b) Detailed sketch of the pixel detector (red) and strip detector (blue) layers [24].

modified. It is comprised of two subsystems: a pixel detector and a strip detector that surrounds it. The most crucial part of the ITk, the pixel detector, is designed with the following set of goals and requirements:

- Area and geometry: The acceptance of a detector is usually expressed by the geometrical parameter of pseudorapidity  $\eta = -\ln \tan \theta/2$  that describes the angle  $\theta$  of a particle relative to the beam axis. The ITk pixel detector extends the tracking coverage to a pseudorapidity of  $|\eta < 4|$  compared to  $|\eta < 2.5|$  of the ATLAS ID. The pixel detector is composed of cylindrical barrels and several end-cap disks covering small  $\theta$  angles. The number of barrel layers have been increased to five in order to cope with the higher rate and improve coverage and tracking performance. The inner layer is placed at a radius of r = 3.6 cm and the outer layer (L4) has a radius of r = 27.3 cm, that is approximately 2 times higher than the outer layer of the ATLAS ID pixel detector. Thus, the total area is significantly higher compared to the ATLAS ID and is estimated to be as large as 12 14 m<sup>2</sup>.

- Hit rate: The HL-LHC luminosity is translated to an increase in the number of interactions per

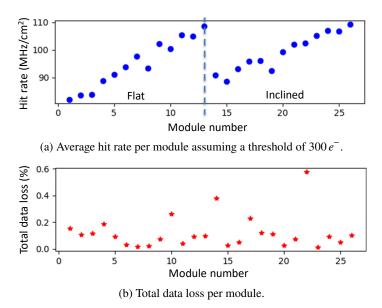

crossing from 20 to about 200 every 25 ns. Therefore, this leads to a high number of pixels being activated (hit) per unit of area and time (hit rate). The average hit rate for the inner layer of the ITk pixel detector is expected to be as high as  $3\,\mathrm{GHz/cm^2}$  while for the outer layer it drops to approximately  $100\,\mathrm{MHz/cm^2}$  which is similar to the hit rate of the inner layers of the current ATLAS pixel detector. To cope with the high hit rate, the pixel size of the ITk has been reduced to  $50\times50\,\mathrm{\mu m^2}$  and a new  $19.2\times20\,\mathrm{mm^2}$  ROIC in 65 nm CMOS technology with high logic density and fast data transmission has been designed by the RD53 collaboration [26].

- Radiation hardness: The radiation tolerance of the sensor and the ROIC is a critical requirement due to the high expected particle flux. As a result of the extreme radiation, the two innermost pixel layers are designed to be replaceable. In the case of the inner pixel layer, the total ionizing dose (TID) over 5 years of operation is expected to be about 500 Mrad and the NIEL fluence is expected to be approximately  $2 \cdot 10^{16} n_{eq}/\text{cm}^2$ . In the case of the outer layer (L4), the requirements are more relaxed and equal to  $50 80 \, \text{Mrad TID}$  and  $1 \cdot 10^{15} 2 \cdot 10^{15} n_{eq}/\text{cm}^2$  NIEL.

- Efficiency and noise occupancy: The hit detection efficiency must be higher than 97% for the whole life-time of the detector, even after the expected radiation dose has been accumulated, and should be achieved while keeping the noise hit occupancy per pixel lower than  $1 \cdot 10^{-6}$  /25ns.

- *Time resolution:* The bunch crossing frequency of the HL-LHC will remain equal to 40 MHz. Therefore, hits should be detected and recorded within 25 ns, otherwise they will be assigned a wrong time stamp and will be regarded as noise.

- Material budget and power consumption: The total material budget should be below 2% in radiation length  $(x/X_0)$  units. Furthermore, the power consumption should remain smaller than  $500 \,\mathrm{mW/cm^2}$  in order to keep the cooling and power delivery requirements reasonable and avoid increasing the material budget.

Hybrid pixels that are being developed based on the RD53 ROIC have been selected for the ITk pixel detector in order to cope with the extreme conditions close to the interaction point. While an implementation of monolithic pixels (DMAPS) for the innermost layers would benefit performance (for example in the case of b and  $\tau$ -tagging) due to their small pixel size and thickness, at present the logic density required for the foreseen hit rate has not been achieved as a result of the feature sizes offered by current CMOS technologies suitable for DMAPS. Furthermore, the radiation hardness that is required by these layers is a serious challenge for current DMAPS designs and has not yet been systematically checked. On the contrary, DMAPS constitute a promising alternative for the outer layer of the ITk pixel detector since it covers the largest area and its radiation and rate requirements are reduced by roughly an order of magnitude compared to the inner layers and are comparable to the present LHC ATLAS pixel detector. It is estimated that the module production cost of the outer layer (L4) can be reduced by about 2.5 MCHF if DMAPS are adopted [23]. Table 2.1 gives a summary of the most important requirements of pixel detectors for the HL-LHC and compares them with representative experiments that can favor different types of pixel technologies.

The DMAPS detector chips developed in the context of this thesis have been designed to target the requirements of ATLAS ITk outer layer (L4), but are also ideally suited for other experiments, such as future upgrades of the Belle II detector where the pixel size, material and power consumption is of utmost importance while other requirements such as radiation hardness and hit rate are more relaxed.

Table 2.1: Comparison of the HL-LHC ATLAS characteristic requirements with representative HEP experiments

|                                      | STAR               | ILC                | ALICE LHC<br>(Heavy-Ion) | ATLAS LHC        | ATLAS I<br>Outer   | HL-LHC<br>Inner  |

|--------------------------------------|--------------------|--------------------|--------------------------|------------------|--------------------|------------------|

| Time resolution (ns)                 | 110                | 350                | 20000                    | 25               | 2.                 | 5                |

| Particle Rate (MHz/cm <sup>2</sup> ) | 0.4                | 25                 | 1                        | 100              | 100                | up to 3000       |

| NIEL Fluence $(n_{eq}/\text{cm}^2)$  | > 10 <sup>12</sup> | > 10 <sup>12</sup> | > 10 <sup>13</sup>       | $2\cdot 10^{15}$ | $1-2\cdot 10^{15}$ | $2\cdot 10^{16}$ |

| TID (Mrad)                           | 0.2                | 0.4                | 0.7                      | 80               | up to 80           | > 500            |

| Pixel pitch (µm <sup>2</sup> )       | 21x21              | _                  | 28x28                    | 50x250           | 50x50              | 50x50            |

| Pixel type                           | MAPS               | _                  | MAPS                     | Hybrid           | Hybrid<br>or DMAPS | Hybrid           |

## **Monolithic Pixel Detector Fundamentals**

Pixel detectors are composed of highly segmented solid-state semiconductor elements. Their basic structure consists of two parts, the sensor where a signal of electron hole pairs (e/h) is generated by ionization from a traversing particle and the readout electronics that process, digitize, store and transmit the hit data. Silicon is by far the most widely used material for semiconductor detectors because it is abundant, stable, has a relatively low bandgap that allows for sufficient charge generation and can also form high quality insulators (SiO<sub>2</sub>). For the detection of charged particles in accelerators such as the LHC, silicon is an ideal material, while for other applications, such as X-ray detection, other semiconductors (e.g. CdTe) provide better absorption characteristics. Readout chips are nearly exclusively produced from silicon, following the microelectronics CMOS technology revolution.

The sensor and the ROIC can be separate entities or integrated in the same silicon crystal leading to two different approaches in the way a pixel can be structured, called hybrid and monolithic respectively. In this chapter, the concept of Depleted Monolithic Active Pixel Sensors (DMAPS) along with its unique characteristics will be described and compared to the state-of-the-art hybrid pixels. To provide a better understanding of the concepts that will be discussed, fundamental principles of silicon detector operation and key performance criteria will be introduced.

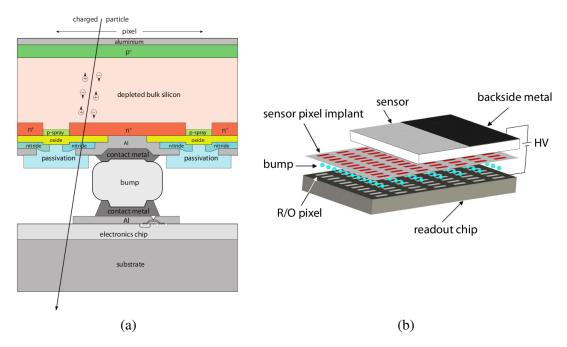

## 3.1 Silicon detector fundamentals and the state-of-the-art: Hybrid pixels

Hybrid pixels have been established as the technology of choice for high occupancy and high radiation environments by the LHC ATLAS and CMS experiments. They are made up of two parts, as shown in Fig. 3.1, which exactly match: The sensor part that is produced in specialized sensor grade silicon material and one or several readout chips with the same cell pattern that are manufactured in standard CMOS processes. Sensor and chip are connected in every pixel using flip-chipping/bump-bonding and 3D integration techniques. As mentioned in Chapter 2, hybrid pixels with sizes down to  $50 \times 250 \, \mu m^2$  have been successfully manufactured with high yield for the LHC, while  $50 \times 50 \, \mu m^2$  size pixels will be installed during the HL-LHC upgrade. The preferred bonding techniques are eutectic soldering and In-In thermocompression. During the initial LHC detector development, a bonding pitch in the scale of 50 um was 15 years ahead of industrial demands. This pitch has become a standard today and connection density down to 25  $\mu$ m has been achieved.

The main benefit of hybrid pixels is that the sensor and the ROIC part can be separately optimized to excel in their specific task: fast, efficient charge collection even after irradiation and low noise,

Figure 3.1: Hybrid pixel detector: a) Individual pixel layout composed of a dedicated sensor and the readout electronics cell connected through a bump-bond, b) Illustration of a hybrid pixel detector matrix [20]

fast, high rate capable and radiation tolerant electronic readout respectively. The disadvantages of the hybrid approach become evident when addressing the requirements of future particle detectors demanding high granularity (small pixel size), low material budget and large area coverage. The bump-bonding process adds an extra step in module manufacturing, is labor intensive and increases cost considerably. Additionally, the vendors providing the specialized sensor wafers do not usually operate large volume production lines increasing cost and turnaround times. The technological limitations are mostly related to the bumping technology and the power density associated with the minimum achievable pixel capacitance and the fact that the electronics circuitry is confined to the same area as the detecting electrode.

#### 3.1.1 The sensor: signal generation and formation

## 3.1.1.1 Energy loss of charged particles

When traversing a medium, charged particles lose energy that can be mainly attributed to a sum of contributions from ionization, atom excitation and bremsstrahlung radiation. The energy being lost by each interaction arises from individual stochastic processes. Therefore, the average energy is used instead which is also called stopping power since it describes how particles are stopped in matter. There are different regions, depending on the passing particle mass and momentum where different energy loss processes dominate and are described by a different theoretical description.

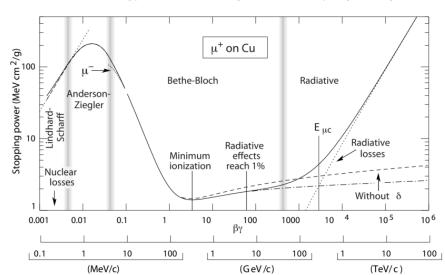

As an example, the dependence of stopping power as a function of  $\beta \gamma = p/mc$  for  $\mu^+$  in copper is given in Fig. 3.2. The energy loss by bremmstrahlung scales with the inverse squared mass of the radiating particle  $(1/m^2)$  [35]. For electrons and positrons, due to their small mass, energy loss by bremmstrahlung becomes relevat at relatively small energies. However, in the case of heavier particles,

the radiation contribution to energy loss becomes significant at very high energies.

Figure 3.2: Stopping power (-dE/dx) for  $\mu^+$  in copper as a function of  $\beta\gamma$ . Each region is described by a different theoretical description. At high energies bremsstahlung (radiative losses) dominate. The center region is described by the Bethe-Bloch formula. For lower energies, the characteristic  $1/\beta^2$  dependence of the Bethe-Bloch formula is no longer valid as quantum mechanical interference effects and energy-depended shell corrections become relevant. For very low energies non-ionizing energy loss caused by elastic nuclear recoil dominates [45].

The energy loss by ionization and atom excitation is given by the Bethe-Bloch formula [35] which accurately describes the central region of energies in Fig. 3.2:

$$\left\langle -\frac{\mathrm{d}E}{\mathrm{d}x} \right\rangle = K \frac{Z}{A} \rho \frac{z^2}{\beta^2} \left[ \frac{1}{2} \ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} - \beta^2 - \frac{\delta(\beta \gamma)}{2} - \frac{C(\beta \gamma, I)}{Z} \right] \tag{3.1}$$

Muon momentum

where:

- $-K = 4\pi N_A r_e^2 m_e c^2$ .  $N_A$  is Avogadro's number,  $m_e$  is the electron mass and  $r_e$  is the classical electron radius ( $\approx 2.8 \text{ fm}$ ).

- $-\zeta$ ,  $\beta$  are the charge and velocity of the projectile particle.

- Z, A are the atomic mass and number of the medium.

- *I* is the mean excitation energy.

- $-T_{max}$  is the maximum energy transfer to a shell electron (central collision).

- $-\delta$  is the so called density correction, important at high energies.

- C/Z is a shell correction factor, relevant for small  $\beta$  values.

At low energies the stopping power is high as the  $1/\beta^2$  term becomes dominant. This dependence can be explained by the fact that momentum transfer increases with the effective interaction time, that is longer for slower particles. At high energies the  $ln\gamma$  term is dominant. The reason of the stopping power rise at high energies is twofold: The first one is the asymptotic increase of the maximum energy transfer  $(T_{max})$  with  $\gamma$  and the second is the increase of the traverse electric field extension

with  $\gamma$  (relativistic effect). In between these regions there is a minimum at about  $\beta\gamma\approx 3-3$ , 5 whose exact value depends on Z. Particles with kinetic energies in this range are called Minimum Ionizing Particles (MIPS). Since the energy loss increase for  $\beta\gamma>3-3$ , 5 is moderate, it is common practice to also refer to particles with energies higher that this minimum as MIPS. The concept of MIPS is very important in pixel detector operation and characterization since most relativistic particles relevant to collider experiments have mean energy loss rates close to this minimum that represents the worst case of the generated signal magnitude.

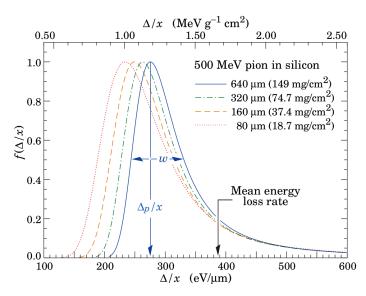

The Bethe-Bloch formula describes the average energy loss per path length. However, since energy loss is statistical in nature, fluctuations occur both in the number of ionization/excitation processes and the emitted energy  $\delta E$  in each process. For relatively thin sensors such as silicon sensors used by pixel detectors, the energy loss probability density function follows a Landau distribution [35] which in practice is often more accurately described by convolution with a Gaussian function. An example of the energy loss distribution in the case of 500 MeV pions in silicon is shown in Fig. 3.3. The energy loss fluctuations lead to a distribution that is asymmetric and is composed of a Gaussian part that corresponds to many ionization processes with small energy loss and a tail that corresponds to high energy loss values. Large energy losses occur due to hard collisions with shell electrons that transfer a high amount of energy to individual electrons, the so called delta electrons. It is worth noting that the Most Probable Value (MPV)  $\Delta_p$  of the energy loss is smaller than the average value ( $\langle dE/dx \rangle$ ) depending on the symmetry of the distribution.

Figure 3.3: Energy loss distribution of 500 MeV pions in silicon, normalized to unity at the MPV. Each curve corresponds to a different sensor thickness. [45]

## 3.1.1.2 Charge generation

When charged particles lose energy by ionization or a photon is absorbed by a semiconductor detector, part of the released energy is used to generate charge carriers in the form of electron-hole (e/h) pairs. In order to create an e/h pair, at least the bandgap energy (in silicon  $\Delta E_{gap} = 1.1 \,\text{eV}$ ) is should be provided. However, since silicon is an indirect band-gap semiconductor, due to momentum

conservation, part of the energy is absorbed by lattice excitations called phonons. The average energy  $w_i$  required to create an e/h pair is temperature dependent. For silicon in 300 K,  $w_i = 3.65$  eV which is about three times higher than the band-gap energy. For a given amount of deposited energy, the average number of e/h pairs generated in silicon is  $N = E/w_i$ . In the case of a minimum ionizing particle traversing a silicon sensor, the MPV of the energy loss is approximately 0.28 keV/um, and in first order does not depend on the sensor thickness. Therefore, the average number of produced e/h pairs is given by:

$$N_{A_p} = \frac{A_p}{w_i} = \frac{0.28 \text{ keV/}\mu\text{m}}{3.65 \text{ eV}} \cdot d(\mu\text{m}) \approx 80 \frac{e/h}{\mu\text{m}} \cdot d(\mu\text{m})$$

(3.2)

where d is the sensor thickness.

For each event, the deposited energy is randomly split between an amount used to generate e/h pairs and an amount that is absorbed by the lattice. Therefore, the number of generated e/h pairs is subject to fluctuations that usually follow a Poisson distribution, which for a large number of processes (>10) resembles a Gaussian distribution. Thus, the standard deviation of the carrier number  $(N_{e/h})$  fluctuation is equal to  $\sigma_{e/h} = \sqrt{N_{e/h}}$ . A special case is the complete absorption of a particle, for example an X-ray photon. Under this constraint, the standard deviation is given by:

$$\sigma_{e/h} = \sqrt{N_{e/h} \cdot F} \tag{3.3}$$

where F is called the Fano factor [35] and determines the ultimate limit of energy resolution for semiconductors. F depends on the material and temperature and for silicon is equal to  $F_{Si} \approx 0.08$ . Therefore, the energy resolution is better than expected from the sheer number of fluctuations.

## 3.1.1.3 Charge transport

The generated e/h pairs are subsequently transported and collected, inducing a signal at the collection node. There are two mechanisms of charge transport in semiconductors, diffusion and drift [35]. Owing to thermal motion, a gradient in the concentration of charge carries leads to a diffusion current which for the density n and p of the electrons and holes, respectively, takes the form:

$$\vec{j}_{n,\text{diff}} = -eD_n \vec{\nabla} n, \qquad \vec{j}_{p,\text{diff}} = -eD_p \vec{\nabla} p$$

(3.4)

where  $D_{n,p}$  is the diffusion coefficient for electrons and holes, respectively, which depends on the semiconductor material. Charge transport by diffusion is slow and does not depend on the electric field. Additionally, due to the thermal random walk, the charge carrier path is usually long. As mentioned in section 2.2, diffusion leads to the spread of the charge cloud and limits the minimum useful pixel size.

In the presence of an electric field, electrons and holes (free charge carriers) are accelerated in the direction of the field while scattering off lattice phonons and crystal defects. In this case the equation of motion for the average electron and hole movement is described by the drift velocity which is equal to:

$$\vec{v}_{Dn} = -\mu_n \vec{E}, \qquad \vec{v}_{Dp} = -\mu_p \vec{E} \tag{3.5}$$

where  $\mu_n$  and  $\mu_p$  is the mobility of electrons and holes respectively. For low fields, the mobility is relatively constant. However, for high fields (approximately higher than  $10^5$  V/cm) it gradually degrades leading to drift velocity saturation ( $v_{sat}$ ). In the case of silicon, typical values for the

electron and hole mobility are  $\mu_n(Si) = 1\,450\,\mathrm{cm}^2/\mathrm{Vs}$  and  $\mu_p(Si) = 500\,\mathrm{cm}^2/\mathrm{Vs}$  respectively while the saturation velocity is equal to  $v_{sat} \approx 10^7\,\mathrm{cm/s}$ . The drift motion of charge carriers leads to a drift current  $\vec{j}_{drift} = \frac{1}{\rho}\vec{E}$ , where  $\rho$  is the electric resistivity given by:

$$\rho = \frac{1}{e(n\mu_n + p\mu_p)} \tag{3.6}$$

For a doped semiconductor, depending on the doping type, the charge carrier density (n,p) is usually defined by the doping concentration  $(N_A,N_D)$  that is usually significantly higher than the intrinsic carrier density. As will be discussed in the following, the resistivity is an important parameter of the sensor that affects the efficiency of charge collection.

Fast charge collection is crucial for high rate and high radiation applications. In the case of the LHC (p-p), all charge carriers have to be collected in a time slot of 25 ns, that is only possible by drift transport. Furthermore, the charge carriers should be collected as fast as possible to avoid signal loss due to trapping or recombination, especially after irriadiation because the induced bulk damage increases the trapping probability.

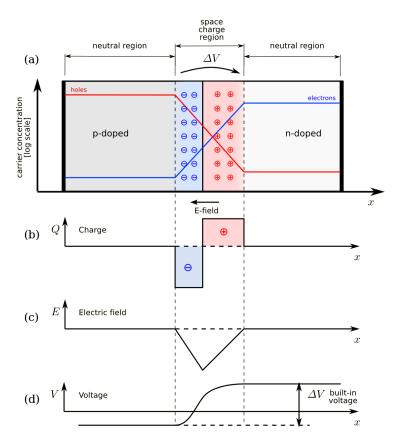

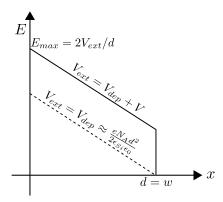

## 3.1.1.4 The p-n junction and sensor depletion